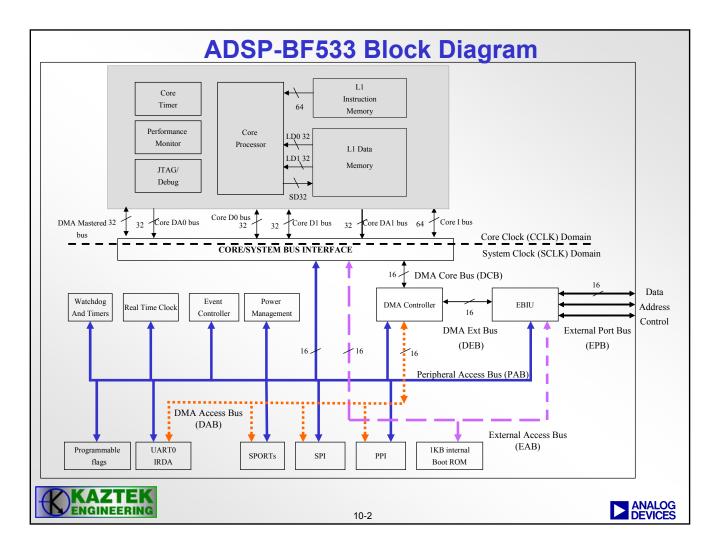

## Section 10

#### Timers and Programmable Flags

10-1

ANALOG DEVICES

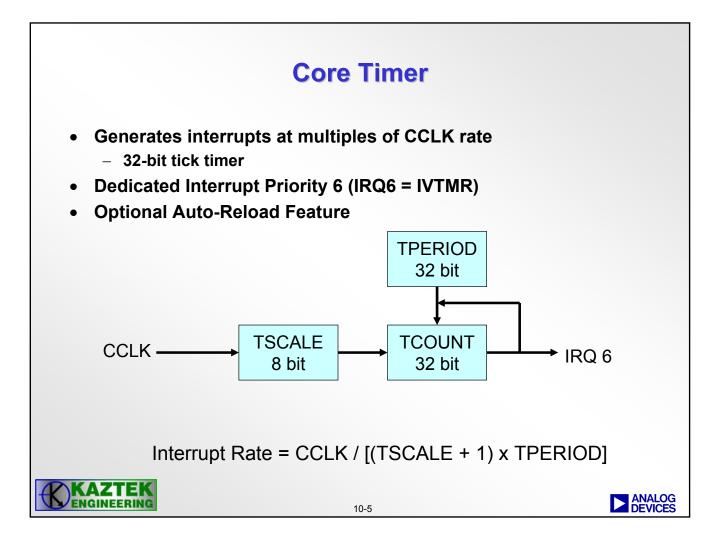

#### **Core Timer**

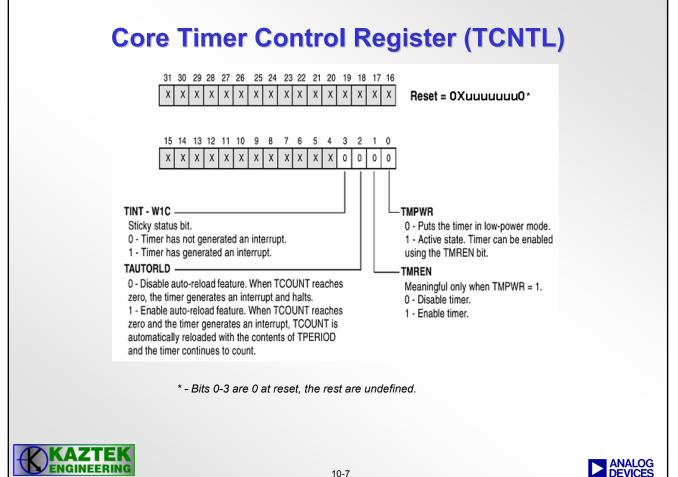

- 3 Bits Enable The Core Timer To Generate Interrupts

- TMPWR, bit 0 in Core Timer Control Register (TCNTL)

- Provides Power To Core Timer

- TMREN, bit 1 in the TCNTL, Enables Core Timer

- IVTMR, bit 6 in the IMASK register, Enables Core Timer Interrupt

- Core Timer Is Halted In Emulator Mode

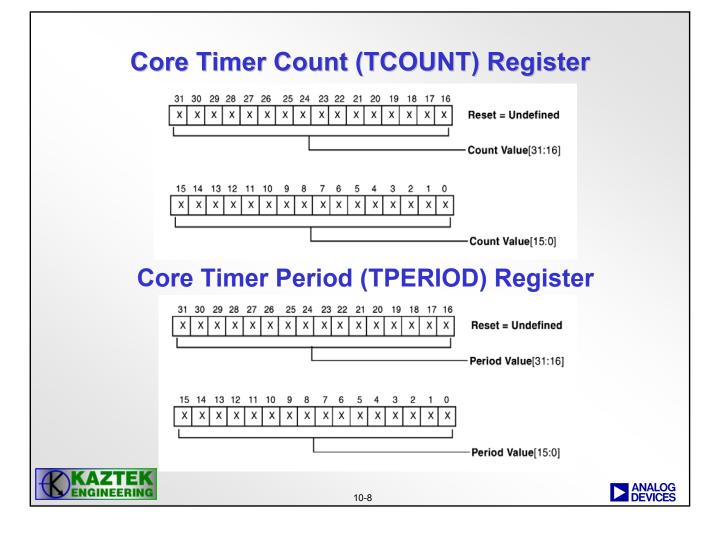

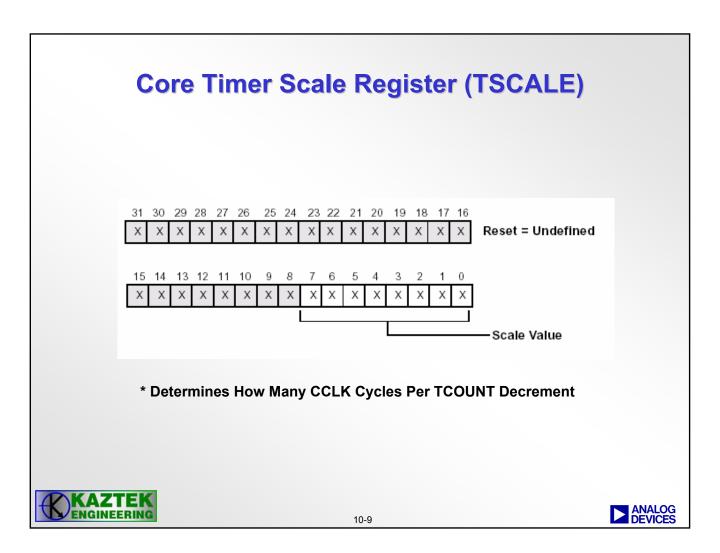

- Timer Scale Register (TSCALE) Controls How Often Timer Count Register (TCOUNT) Is Decremented

- TCOUNT decrements once every TSCALE+1 CCLK cycles

- When TCOUNT Decrements to Zero

- Interrupt is generated

- Write 1 to TINT (bit 3 in TCNTL) to clear interrupt

- If auto-reload is enabled (TAUTORLD, bit 2 in TCNTL)

- TCOUNT reloaded with Timer Period Register (TPERIOD)

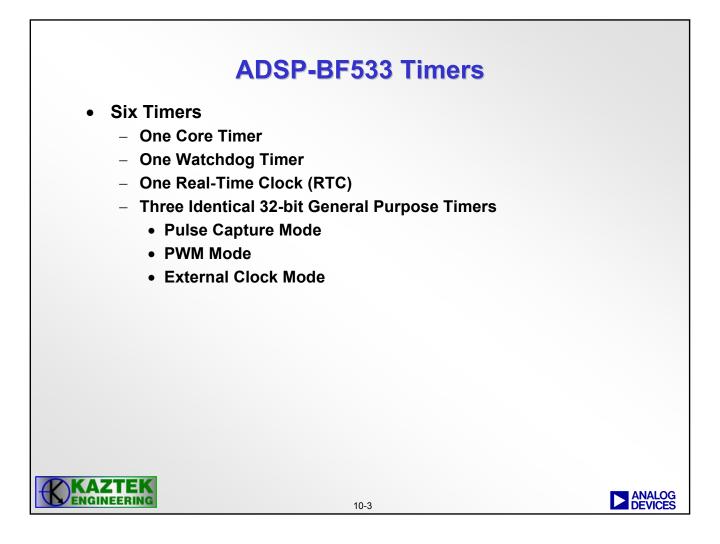

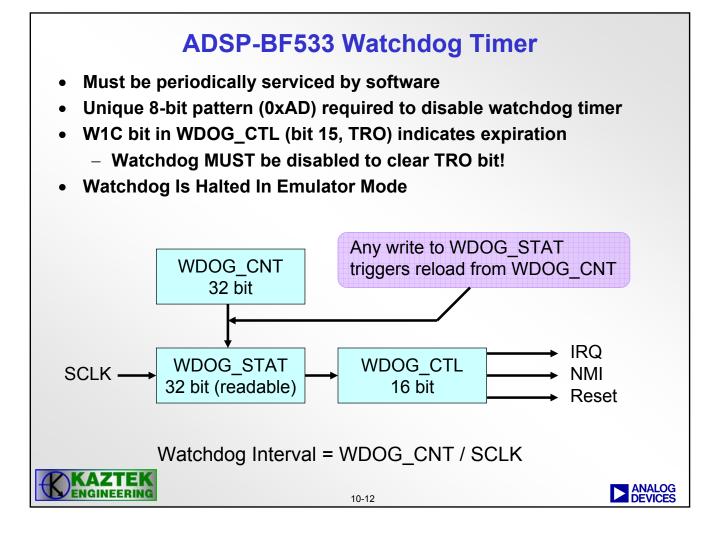

### **ADSP-BF533 Watchdog Timer**

- Peripheral Timer Clocked By The System Clock (SCLK)

- Used To Improve System Reliability By Generating An Event When The Timer Expires Before Being Updated By Software

- Type Of Event Generated By Watchdog Is Programmable In Watchdog Control (WDOG\_CTL) Register

- Reset (software reset takes place)

- NMI (non-maskable interrupt occurs)

- General Purpose Interrupt (IVG13, by default)

- Enable Watchdog Timer To Generate Interrupts

- Set Software Watchdog Timer Interrupt Bit (bit 20 in SIC\_IMASK)

- Set IVG13 (bit13 in IMASK register), by default

- When interrupt priority is reassigned, the IVGx bit changes

- Enable timer and type of event generated in WDOG\_CTL

10-11

| Watchdog Control Register (WDOG_CCL         Watchdog control Register (WDOG_CTL)                                                                                                                                                                                                                                                                                                                                                                                             | _) |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| enabled When ICTL[1:0] is set to generate a reset event, bit 15 of the WDOG_CTL register is cleared and the Software Watchdog Timer Source bit in the SWRST register is set when the watchdog timer expires. The SWRST register is discussed further in the System Design chapter. When ICTL[1:0] is set to generate an NMI or GP interrupt, bit 15 of the WDOG_CTL register is sticky and must be cleared in the Interrupt Service Routine when the watchdog timer expires. |    |

Г

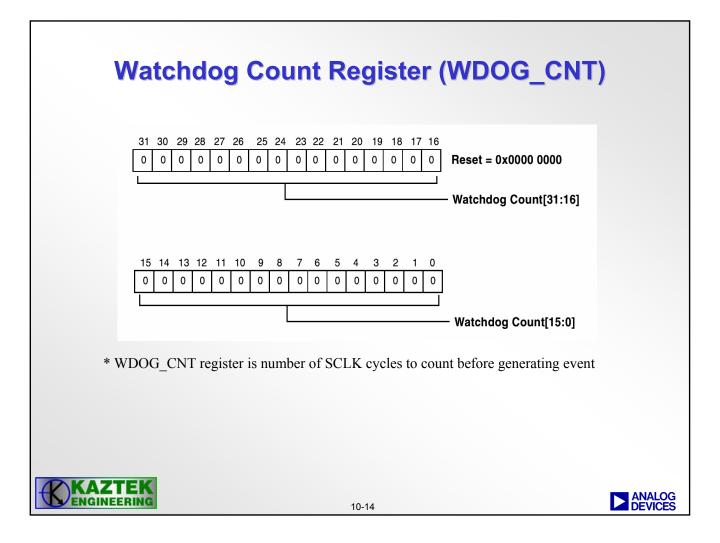

| v      | Vatchdog Status Register (WDOG_STAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -)                |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|        | 31       30       29       28       27       26       25       24       23       22       21       20       19       18       17       16         0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0 |                   |

|        | 15       14       13       12       11       10       9       8       7       6       5       4       3       2       1       0         0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0   |                   |

|        | * Reads Of WDOG_STAT Return Current Count Value<br>* Writes To WDOG_STAT Reload WDOG_STAT With WDOG_CNT Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

| ENGINE | <b>ERING</b> 10-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ANALOG<br>DEVICES |

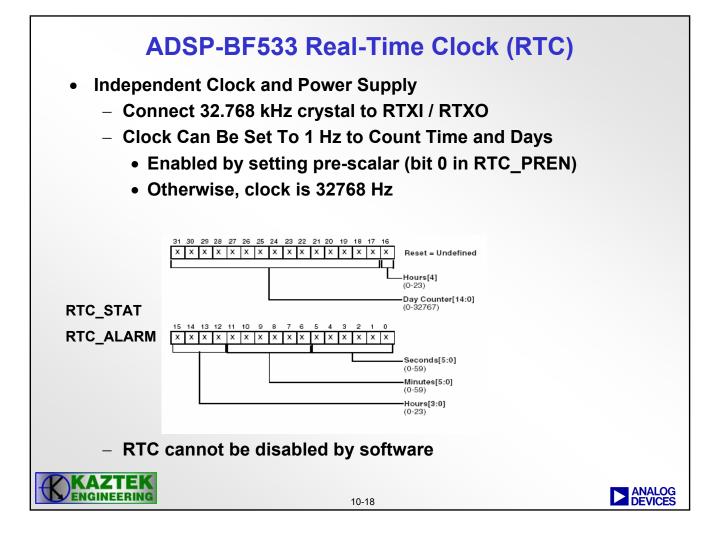

#### **Real-Time Clock Features**

- Provides digital watch features to the processor

- Time of day, alarm, and stopwatch count-down

- Typically used to implement real-time watch or "life counter"

- Counts the elapsed time since last system reset

- Uses dedicated power supply pins

- Independent of any reset

- Maintains functionality even when rest of processor is powered down

#### • Primary function is to maintain time of day using 4 counters

- Seconds, Minutes, Hours, Days

- Each of the 4 counters can generate an interrupt

- Each interrupt is independently controlled

- Equipped With Two Alarm features

- Daily and Day-And-Time

- Each has its own independently-controlled interrupt

10-17

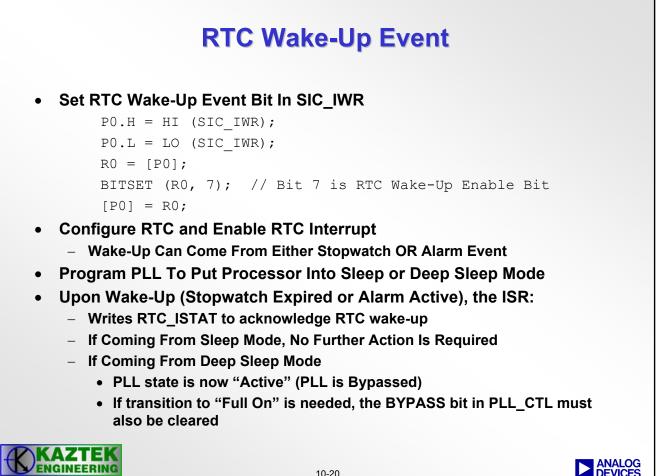

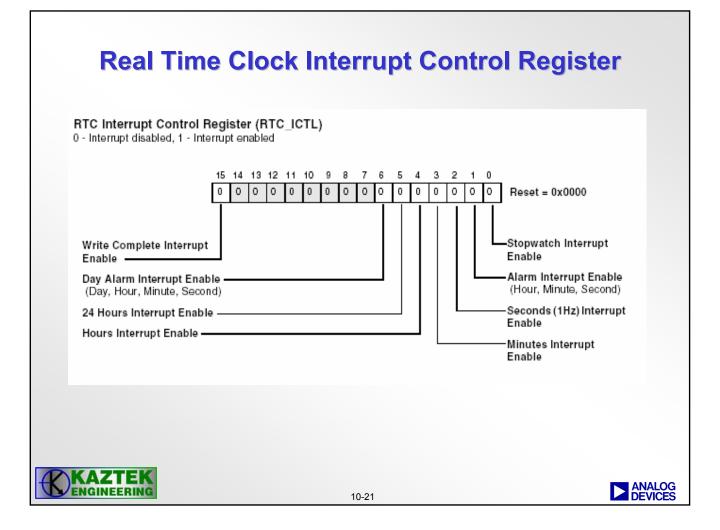

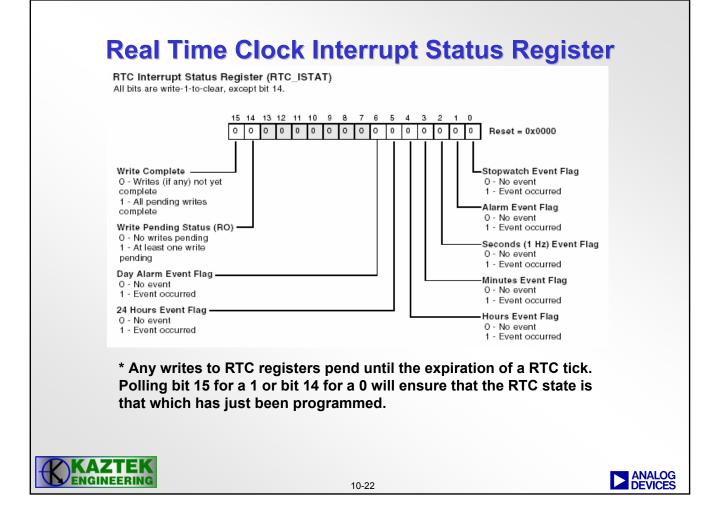

#### **ADSP-BF533 RTC Interrupts**

- RTC Interrupt May Be Issued Based On 7 Different Events

- Interval interrupts

- Every Second, Minute, Hour, and/or Day

- Alarm interrupts (single or daily)

- Single occurs when RTC\_ALARM matches RTC\_STAT

- Daily recurs when all non-day fields match

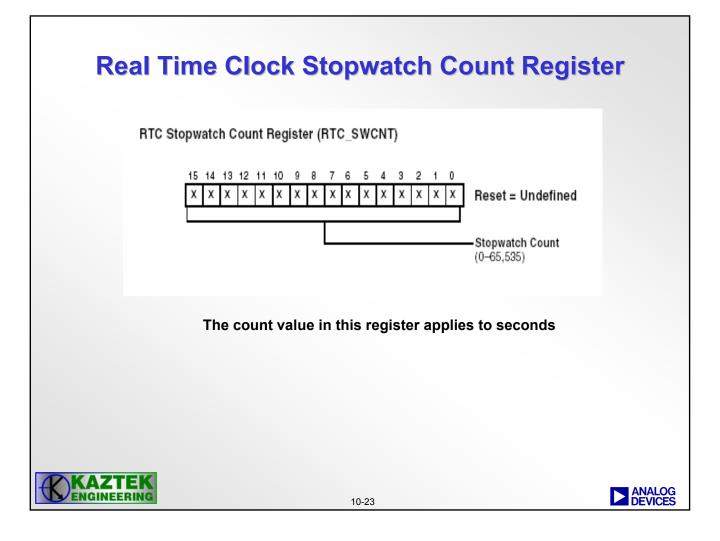

- Stopwatch interrupt

- 16-bit counter (RTC\_SWCNT) decrements every RTC tick

- Period of up to 18 hours, 12 minutes, and 15 seconds

- Interrupt when RTC\_SWCNT reaches zero, no autoreload

- RTC Interrupt Can Be Used To Wake Processor From Sleep Modes

| Real T       | ime Clock Prescaler Enable Regist                                                                            | er                |

|--------------|--------------------------------------------------------------------------------------------------------------|-------------------|

| Prescaler En | nable Register (RTC_PREN)                                                                                    |                   |

|              | 4 13 12 11 10 9 8 7 6 5 4 3 2 1 0<br>0 0 0 0 0 0 0 0 0 0 0 0 0 X Reset = Undefined<br>Prescaler Enable (PREN | )                 |

|              | When bit 0 is set, the RTC runs at 1 Hz.                                                                     |                   |

|              | When bit 0 is cleared, the RTC runs at 32.768 kHz.                                                           |                   |

|              |                                                                                                              |                   |

|              | 10-24                                                                                                        | ANALOG<br>DEVICES |

# **General Purpose Timers** ANALOG DEVICES NGINEERI 10-25

#### **Three Peripheral Timers of the ADSP-BF533**

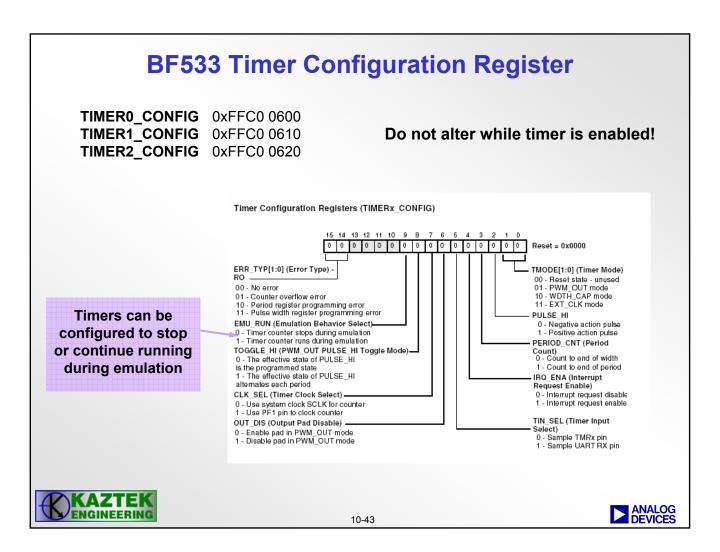

- Three Identical Timers Can Be Configured In 3 Modes

- Pulse Width Modulation (PWM\_OUT)

- Width and Period Capture (WDTH\_CAP)

- External Event Counter (EXT\_CLK)

- Dedicated Pins TMR2, TMR1, TMR0

- One Programmable Interrupt Each

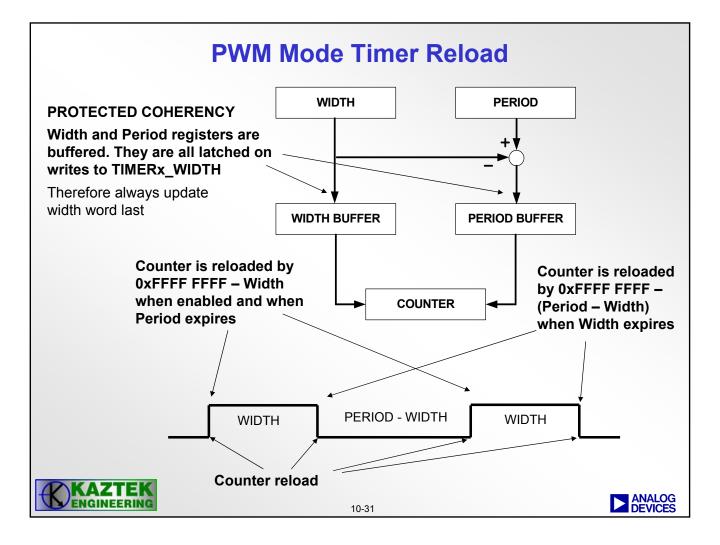

- Three 32-bit Registers Each

- Width (TIMERx\_WIDTH)

- Period (TIMERx\_PERIOD)

- Counter (TIMERx\_COUNTER) (read-only)

- One 16-bit Configuration Register Each (TIMERx\_CONFIG)

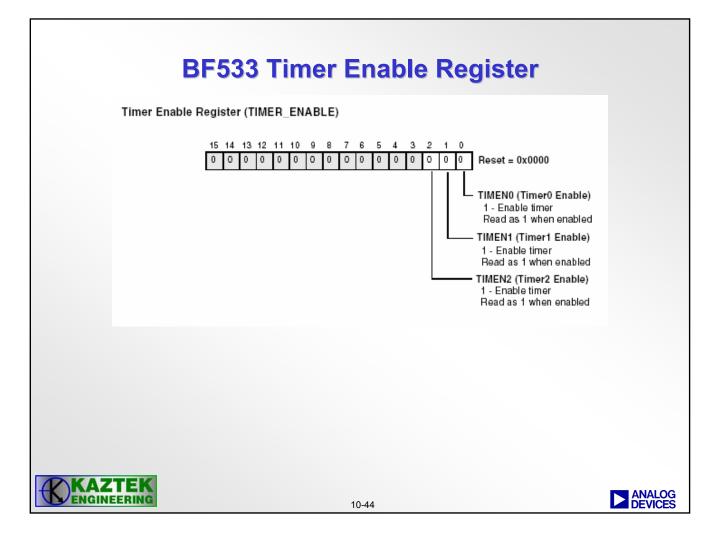

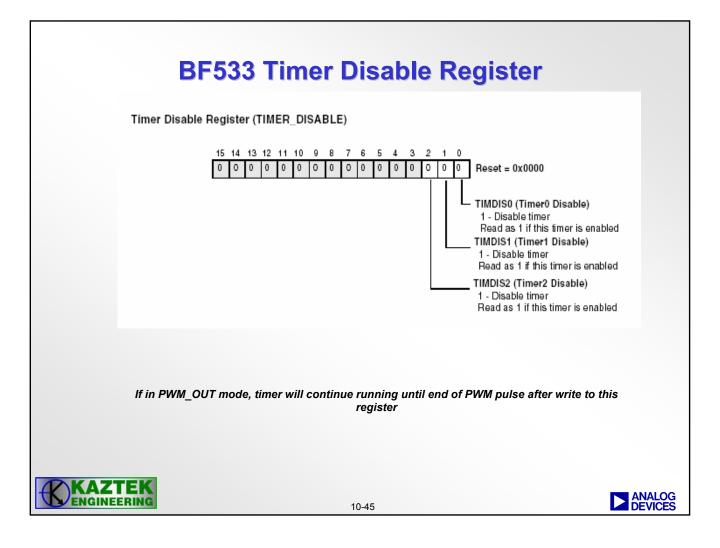

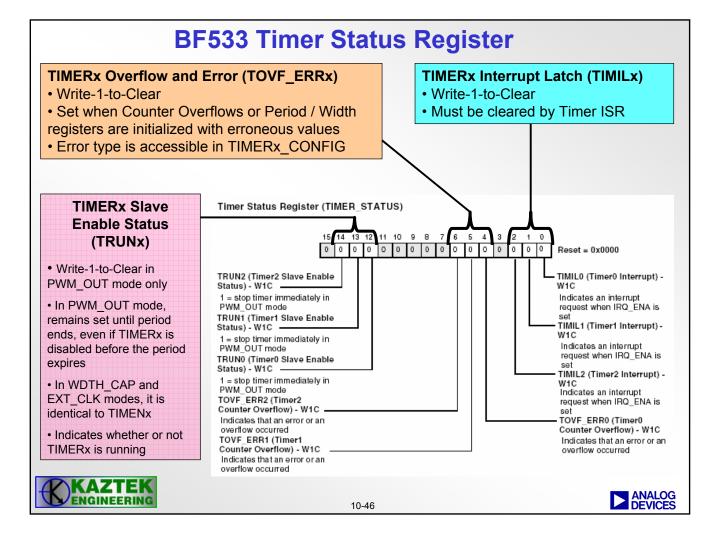

- Three Common Registers Affect All 3 Timers Simultaneously

- Timer Enable

- Timer Disable

- Timer Status (Interrupt requests, overflows, slave enables)

10-26

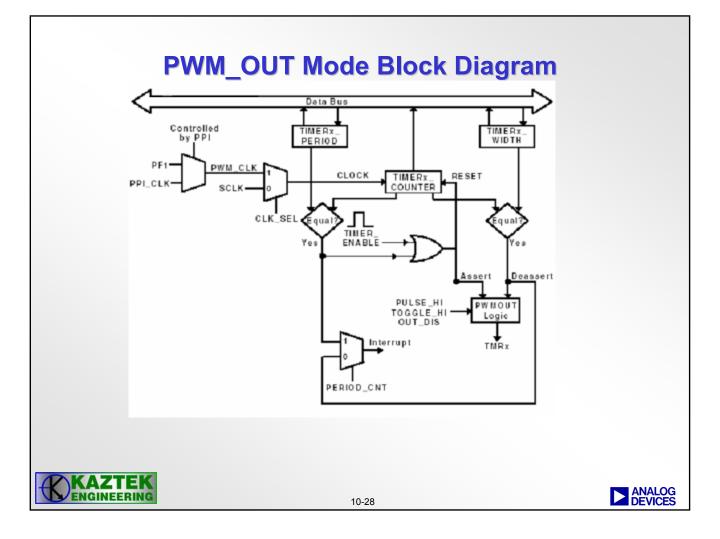

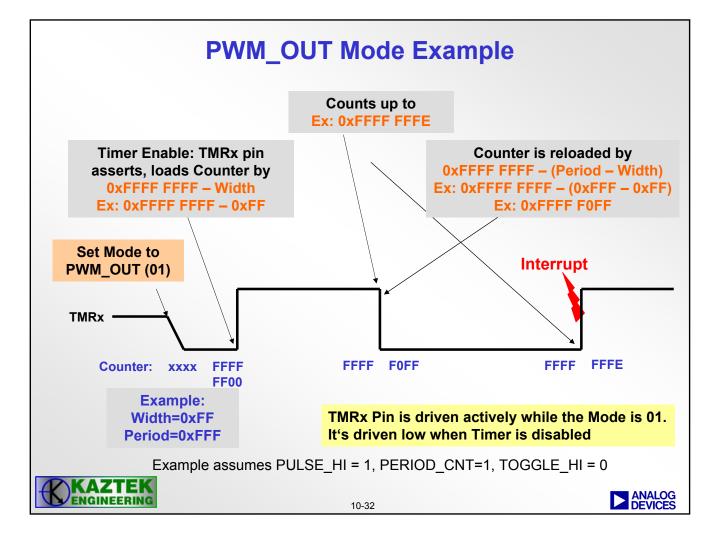

#### **PWM\_OUT Mode**

- Timers clocked from one of three sources

- Internally using SCLK

- Internally by PPI Clock when PPI is enabled

- Externally using PF1 pin when PPI is disabled

- TMRx pins are outputs by default

- Can be tristated using OUT\_DIS in TIMERx\_CONFIG, which reduces power consumption when the output signal is not in use

- Two PWM\_OUT modes

- PWM Waveform Generation (PERIOD\_CNT = 1)

- Interrupt when Period expires

- Use this mode for generating periodic interrupts

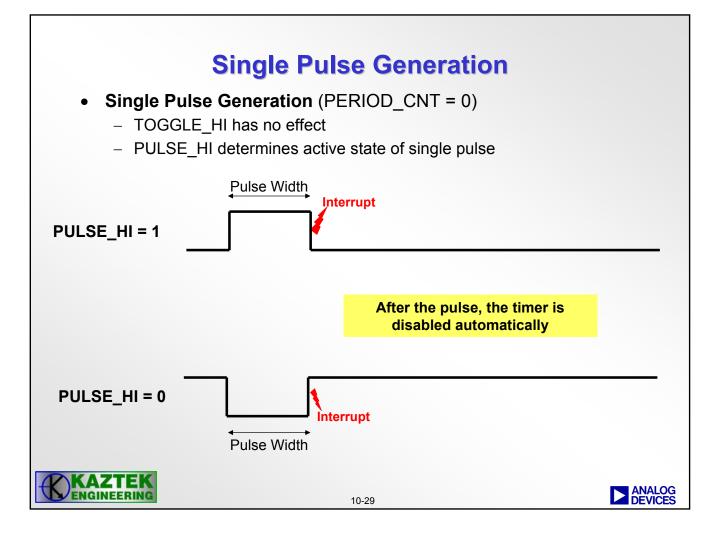

- Single Pulse Generation (PERIOD\_CNT = 0)

- Stops and disables itself after first Pulse Width expires

- Interrupt when Pulse Width expires

- Use this mode for programmable software delay

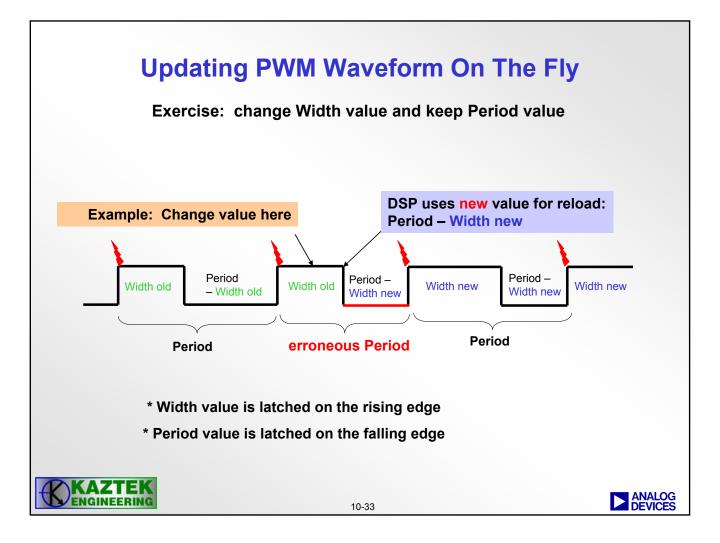

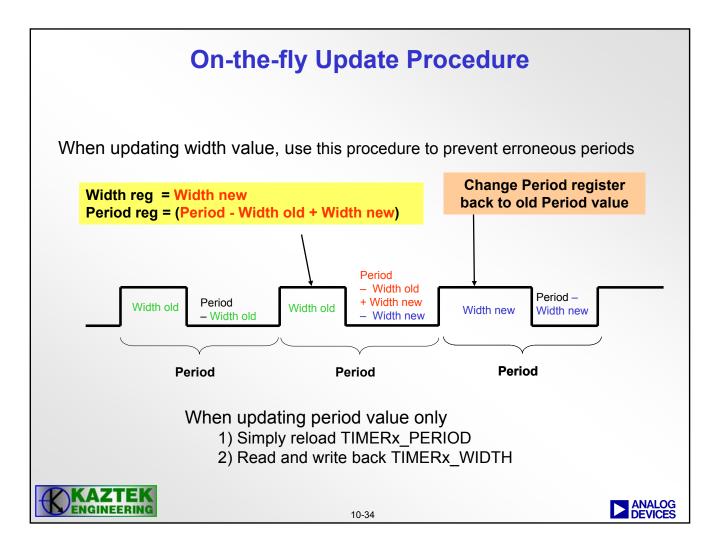

#### **Waveform Generation PWM Waveform Generation** (PERIOD CNT = 1) - TMRx pin polarity is programmable (PULSE\_HI bit) - Toggle Waveform Every Period or Every Other Period (TOGGLE\_HI bit) - Period and Pulse Width adjustable - On-the-fly Update Procedure Period Pulse Width Interrupt Interrupt PULSE\_HI = 1 TOGGLE HI = 0 Interrupt PULSE\_HI = 1 TOGGLE\_HI = 1 Interrupt IGINEER 10-30

| Disabling the Timer                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Example Timer Disable Timing (PWM_OUT mode, PERIOD_CNT=1)                                                                                                                                                                                                                                                               |

| SCLK                                                                                                                                                                                                                                                                                                                    |

| TIMER DISABLE                                                                                                                                                                                                                                                                                                           |

| <ul> <li>INMER_DISABLE</li> <li>In PWM_OUT mode, timer will run to the end of a cycle if TIMER_DISABLE bit set         <ul> <li>TIMER_DISABLE bit set</li> <li>TIMENx will reflect disable, but TRUNx indicates timer is running</li> <li>Timer can be stopped immediately by clearing TRUNx bit</li> </ul> </li> </ul> |

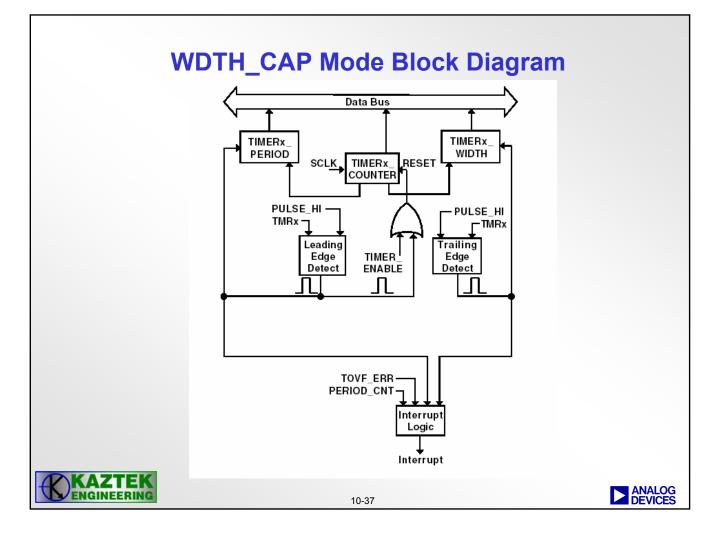

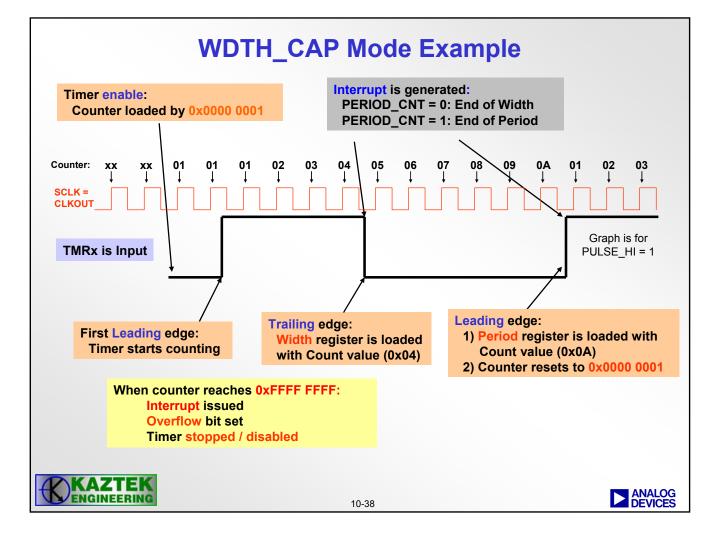

## WDTH\_CAP Mode

- Timers are clocked internally (SCLK)

- TMRx pins are inputs

- PULSE\_HI (active high or low)

- TIN\_SEL (capture TMRx or UART RX)

- Period and Width are counted at the same time

- Flexible Interrupt generation

- PERIOD\_CNT (End of Width or end of Period)

- Period and Width registers are read-only

- To enable (synchronization latency)

- Set to WDTH\_CAP mode

- Add SSYNC

- Set TIMENx in TIMER\_ENABLE (timer starts 3 SCLK cycles later)

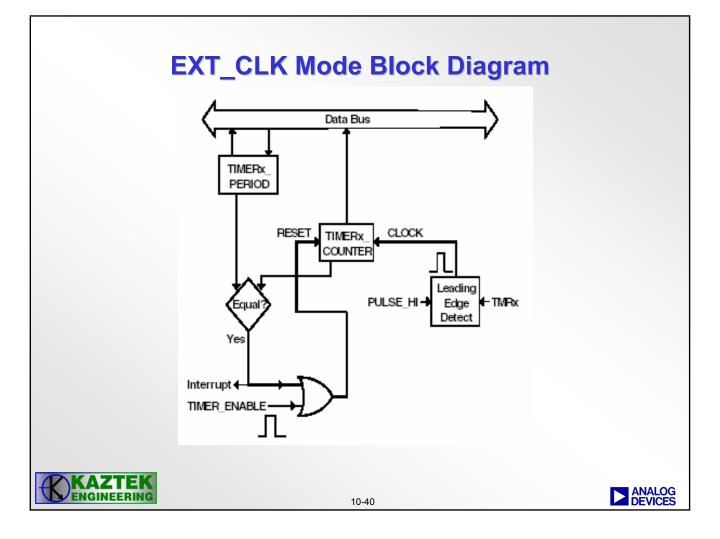

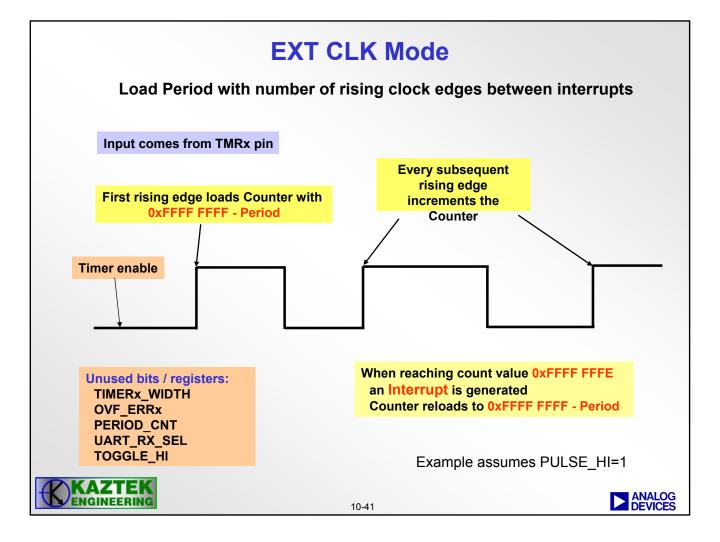

# EXT\_CLK Mode External Clock through input TMRx Pins Clock counts rising or falling edges • Width Register is unused • Period Register is Read/Write • When Period expires, interrupt or wake-up event is generated (if enabled) 10-39

### **BF533 32 Bit Timer Registers**

TIMER0\_COUNTER TIMER1\_COUNTER TIMER2\_COUNTER

TIMER0\_PERIOD TIMER1\_PERIOD TIMER2\_PERIOD

TIMER0\_WIDTH TIMER1\_WIDTH TIMER2\_WIDTH 0xFFC0 0604 0xFFC0 0614 0xFFC0 0624 0xFFC0 0608

0xFFC0 0618 0xFFC0 0628

0xFFC0 060C 0xFFC0 061C 0xFFC0 062C

When disabled, the Counter retains its state. Enabling the Timer initializes the Counter.

10-42

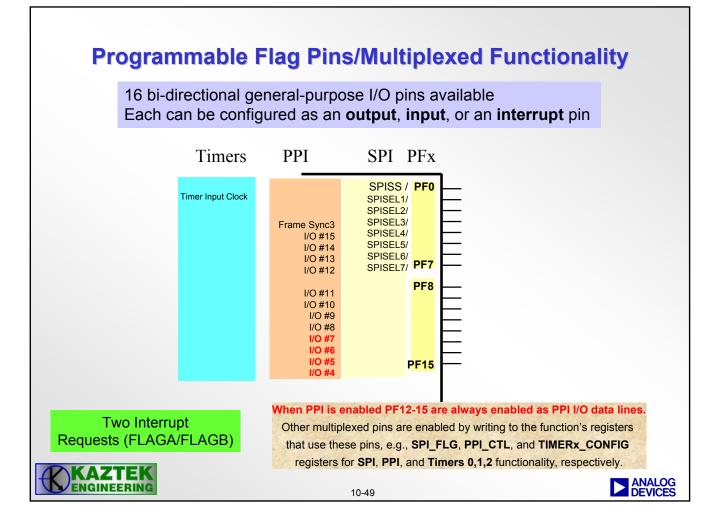

## **Programmable Flags**

### • Features:

- 16 bi-directional general purpose programmable flags

- Each flag pin can be configured as Input or Output

- Two independent interrupt channels (A/B)

- Level or edge sensitive trigger of input source

- Rising or falling edge trigger of input source

- Single edge or both edges trigger of input source

10-48

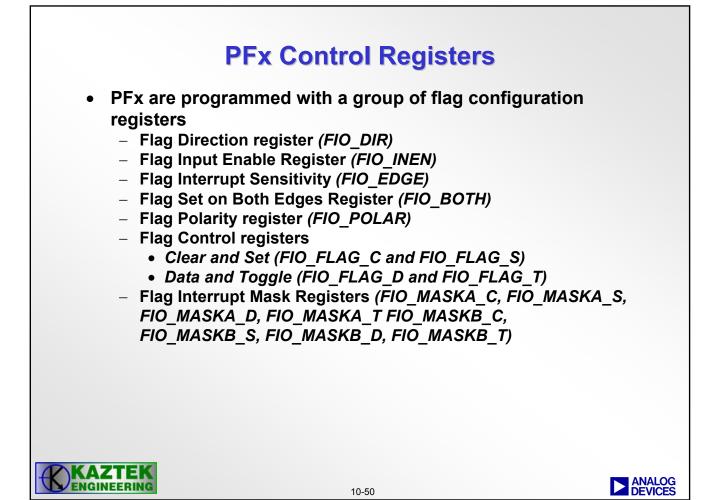

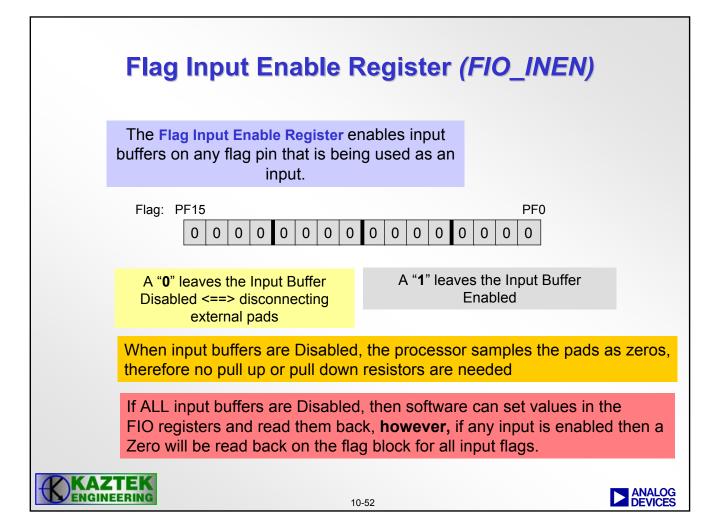

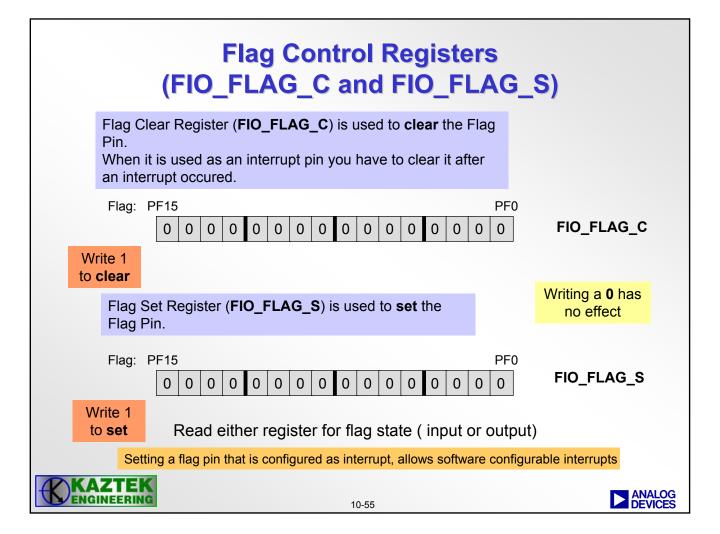

| Flag Direction Register (FIO_DIR)<br>Configures a flag pin as an <i>Input</i> or <i>Output</i>                                                                      |                         |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|--|

| Each bit of the FIO_DIR register<br>corresponds with each of the 16<br>available flag pins                                                                          |                         |  |  |  |

|                                                                                                                                                                     | Reset = 0x0000          |  |  |  |

| Flag: PF15<br>0 0 0 0 0 0 0 0 0<br>Bit: 15                                                                                                                          | PF0 0 0 0 0 0 0 0 0 0 0 |  |  |  |

| <ul> <li>Writing a "1" to a bit of the FIO_D configures the corresponding flag output;</li> <li>Writing a "0" configures the corres flag pin as an input</li> </ul> | pin as an               |  |  |  |

|                                                                                                                                                                     | 10-51                   |  |  |  |

| -                                                                                       | ar                                          | sitivity (FIO_E<br>nd<br>s Register (FI                                  |                       |

|-----------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------|-----------------------|

| Flag Interrupt Sensite the Flag pins for                                                | • •                                         | (FIO_EDGE) specifi edge sensitivity.                                     | ies                   |

| Flag: PF15                                                                              | 0 0 0 0 0                                   | PF0<br>0 0 0 0 0 0                                                       | FIO_EDGE              |

| sensitive,                                                                              | a "1" as an edge                            |                                                                          |                       |

| Flag Set on Both Ec<br>sensitivity                                                      | <b>lges Register (</b><br>for either one or |                                                                          | res                   |

| Flag: PF15                                                                              | 0 0 0 0 0                                   | 0 0 0 0 0 0                                                              | FIO_BOTH              |

| A "1" configures the corres<br>for <b>both-edges sensitiv</b><br>request is generated o | vity. An interrupt                          | A " <b>0</b> " configures Fla<br>falling-edge sensitivit<br>value in FIC | ty (determined by the |

| KAZTEK                                                                                  | 10                                          | )-53                                                                     |                       |

|        | Flag Polarity Regi                                                                                                   | ster (FIO_POLAR)                                                                                                    |

|--------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|        | The Flag Polarity Register select high or low polarity of an input                                                   |                                                                                                                     |

|        | Flag: PF15                                                                                                           | PF0<br>0 0 0 0 0 0 0 0 0                                                                                            |

|        | A " <b>0</b> " configures the corresponding<br>flag pin as <b>active high</b> or <b>rising</b><br><b>edge</b> input. | A " <b>1</b> " configures the corresponding<br>flag pin as <b>active low</b> or <b>falling</b><br><b>edge</b> input |

|        | Flag Polarity applies for Flag P                                                                                     | ins used as inputs or interrupts                                                                                    |

|        | TEK                                                                                                                  |                                                                                                                     |

| ENGINE |                                                                                                                      | D-54 ANALOG DEVICES                                                                                                 |

| Flag Data Register (FIO_FLAG_D)<br>and<br>Flag Toggle Register (FIO_FLAG_T) |                                                                      |                   |  |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------|--|

|                                                                             | g Data Register (FIO_FLAG_D)<br>specifies the state of all PFx pins. |                   |  |

| Flag: PF15                                                                  | PF0<br>0 0 0 0 0 0 0 0 0 0 0 0 0 0                                   | FIO_FLAG_D        |  |

| A "0" clears the state                                                      | e of the pin. A "1" sets the state of t                              | he pin.           |  |

| -                                                                           | oggle Register (FIO_FLAG_T)<br>es the state of all PFx pins.         |                   |  |

| Flag: PF15                                                                  | PF0<br>0 0 0 0 0 0 0 0 0 0 0 0 0                                     | FIO_FLAG_T        |  |

|                                                                             | Write a 1 to toggle                                                  |                   |  |

|                                                                             | 10-56                                                                | ANALOG<br>DEVICES |  |

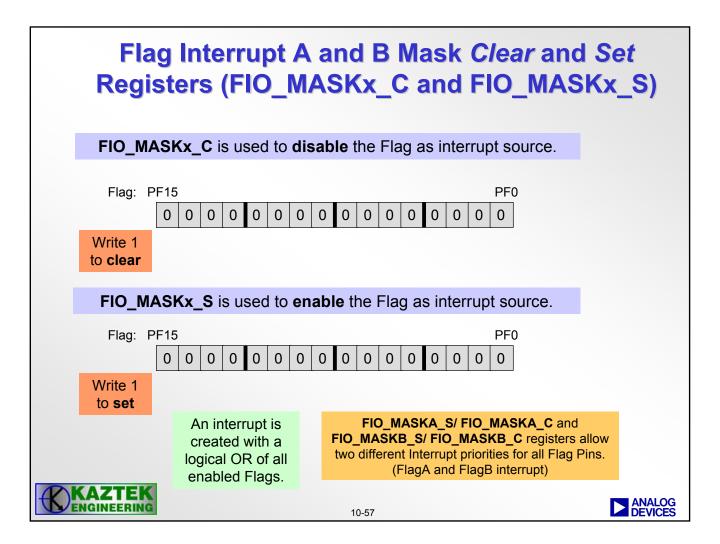

| Flag Interrupt A and B Mask <i>Data</i> and 7<br>Registers (FIO_MASKx_D and FIO_MAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| FIO_MASKx_D is used to directly specify the mask value of the<br>Flag(s) as interrupt source(s).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |

| Flag:       PF15       PF0         0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0 <t< th=""><th></th></t<> |                   |

| FIO_MASKx_T is used to toggle the state of the interrupt mask of the Flag(s) as interrupt source(s).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |

| Flag:       PF15       PF0         0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0 <t< th=""><th></th></t<> |                   |

| Write 1<br>to<br>toggle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |

| TOKA 7TEK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |

| 10-58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ANALOG<br>DEVICES |

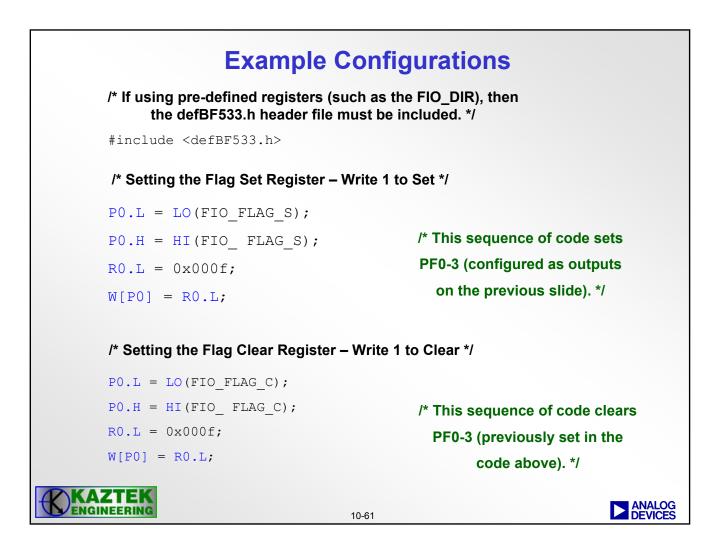

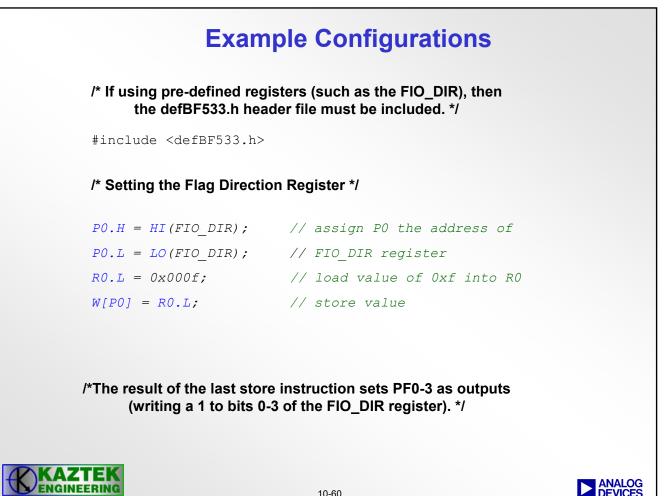

# <section-header><section-header><section-header><list-item><list-item><list-item><list-item>

10-59

10-60