### **Section 16**

System Design

### **Operating Modes**

### **Operating Modes**

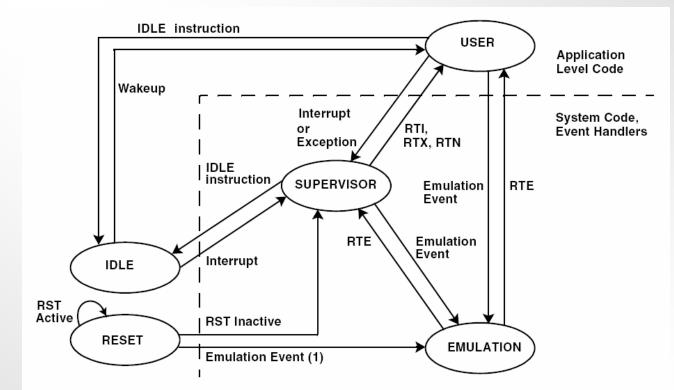

### User mode

Causes exceptions when protected resources are accessed. May be used for algorithm/application code

### Supervisor mode

has unprotected access to all resources. May be used for O/S kernel, device drivers, debuggers, ISRs

### Emulator (or Debug) mode

has supervisor abilities and is accessible via JTAG

Operating Modes provide a feature to implement RTOS architectures and Multitasking schemes. Smaller applications may simply run in Supervisor mode all the time.

# **Operating Modes**

(1) Normal exit from Reset is to Supervisor mode. However, emulation hardware may have initiated a reset. If so, exit from Reset is to Emulation.

### **Power Management Options**

- Low Active Power

- Flexible power management with automatic power-down for unused peripheral sections

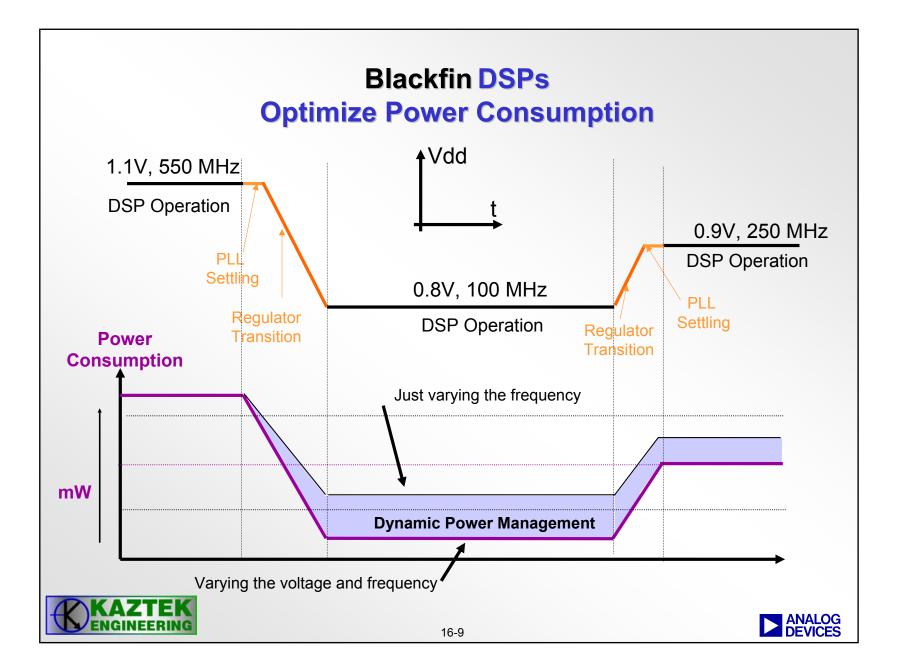

- Dynamic Power Management allows dynamic modification of both frequency and voltage

- Low Standby Power

- 4 Power modes

- Real Time Clock with alarm and wakeup features

### **Dynamic Power Management**

- Clocks to unused • peripherals are automatically disabled.

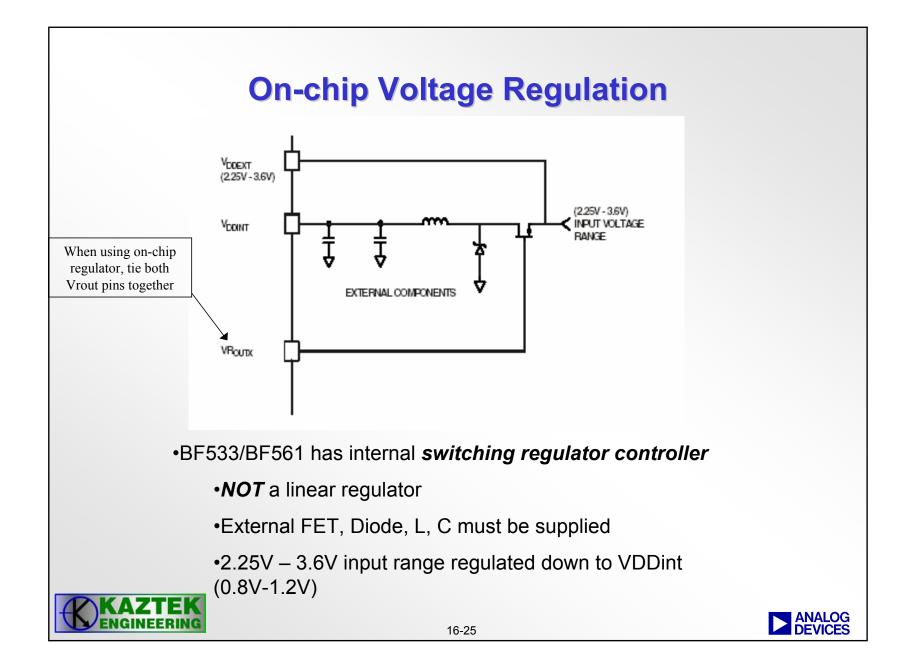

- **Integrated Switching** • **Regulator Controller**

- SW-based Voltage-**Scaling Capability**

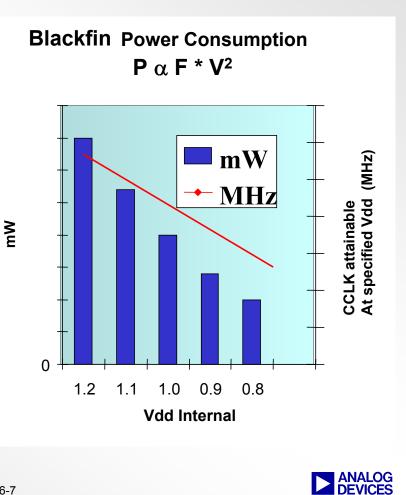

### Blackfin DSPs Control Voltage & Frequency

- Onboard, software-controlled switching regulator controller

- Highly flexible 1x-64x PLL allows easy frequency scaling

- Multiple Power-Down Modes

- Functional & Peripheral Blocks are Clocked Only When Used

Dynamic Power Management Using RTOS or Firmware

| Function                           | Example<br>MHz | Example<br>Vdd (V) |

|------------------------------------|----------------|--------------------|

| F <sub>0</sub> (x)                 | 550            | 1.1                |

| <b>F</b> <sub>1</sub> ( <b>y</b> ) | 250            | 0.95               |

| F <sub>n</sub> (z)                 | 100            | 0.8                |

Profiling Tools Audit MIPS Requirements By Function

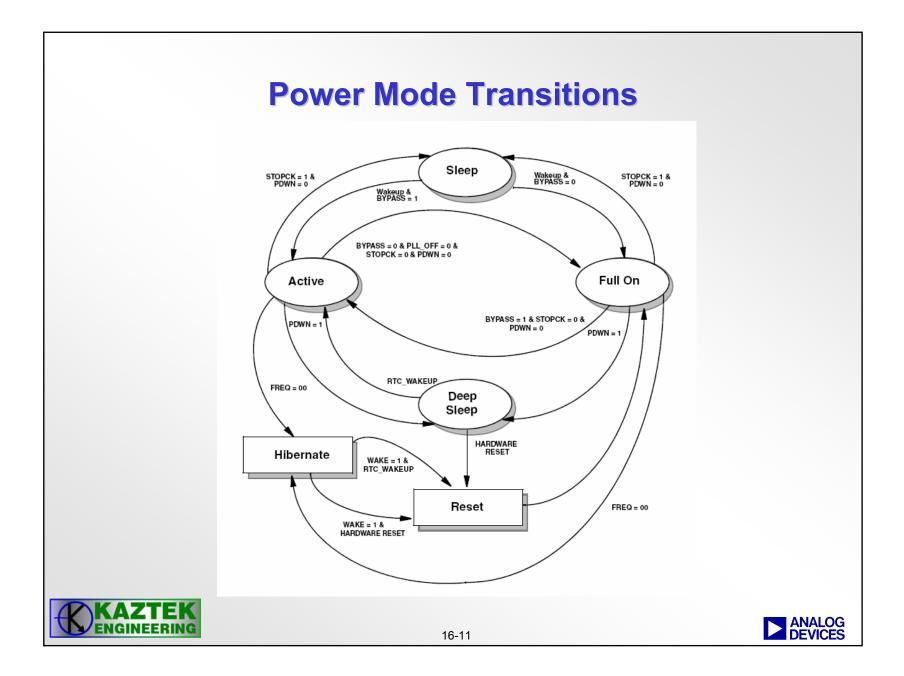

### **Power Management States**

| Mode       | Relative Power<br>Savings | Notes                                                                                                |

|------------|---------------------------|------------------------------------------------------------------------------------------------------|

| Full On    | Min                       | Max performance                                                                                      |

| Active     | Low                       | Full core operation at CLKIN.<br>System DMA to L1 supported.<br>PLL is bypassed and can be disabled. |

| Sleep      | High                      | Core idle. CCLK disabled. SCLK enabled.                                                              |

| Deep Sleep | Very High                 | Core idle. Only Real-Time Clock enabled.<br>Exit only via HW reset or RTC interrupt.                 |

| Hibernate  | Мах                       | VDDINT is disabled. Only VDDEXT<br>applied.<br>Power up via HW reset or RTC interrupt.               |

### **Clock States in Different Power Modes**

| Mode                                  | PLL                    | PLL Bypassed? | Core Clock<br>(CCLK) | System Clock<br>(SCLK) |

|---------------------------------------|------------------------|---------------|----------------------|------------------------|

| <u>Full On</u>                        | Enabled                | No            | Enabled              | Enabled                |

| <u>Active</u>                         | Enabled or<br>Disabled | Yes           | Enabled              | Enabled                |

| <u>Sleep</u>                          | Enabled                | No            | Disabled             | Enabled                |

| <u>Deep Sleep</u><br><u>Hibernate</u> | Disabled               |               | Disabled             | Disabled               |

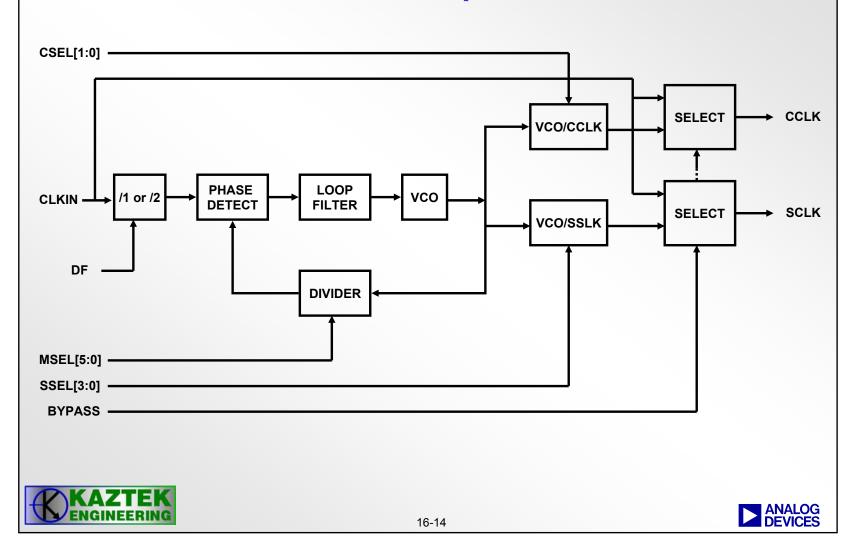

## **BF533 Clocking**

- The BF533 has 2 internal clock domains: CCLK (core clock) and SCLK (system clock)

- CCLK is divided down from the PLL VCO frequency (via CSEL bits in PLL\_DIV), or equals the CLKIN pin frequency if the PLL is bypassed

- SCLK is divided down from the PLL VCO frequency (via SSEL bits in PLL\_DIV), or equals the CLKIN pin frequency if the PLL is bypassed

- SCLK must not exceed 133 MHz

- CLKIN can be driven from external oscillator or crystal

- Programmable PLL supports 1x to 64x frequency multiplication, enabling high-speed operation with low-frequency clock inputs

- Program via bits in PLL\_CTL register

### **Phase-Locked Loop Architecture**

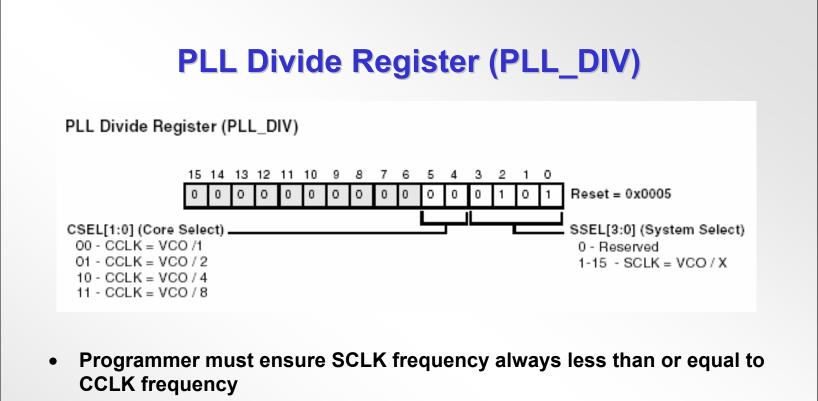

### **CCLK Ratio Control**

| Signal Name | Divider Ratio | Example Frequency Ratios<br>(MHz) |      |

|-------------|---------------|-----------------------------------|------|

| CSEL[1:0]   | VCO/CCLK      | VCO                               | CCLK |

| 00          | 1             | 300                               | 300  |

| 01          | 2             | 600                               | 300  |

| 10          | 4             | 600                               | 150  |

| 11          | 8             | 400                               | 50   |

•Upon reset, CSEL[1:0] = 00

### **SCLK Ratio Control**

| Signal Name | Divider Ratio | Example Free<br>(MHz) | Example Frequency Ratios (MHz) |  |

|-------------|---------------|-----------------------|--------------------------------|--|

| SSEL[3:0]   | VCO/SCLK      | VCO                   | SCLK                           |  |

| 0000        | Reserved      | N/A                   | N/A                            |  |

| 0001        | 1:1           | 100                   | 100                            |  |

| 0010        | 2:1           | 200                   | 100                            |  |

| 0011        | 3:1           | 400                   | 133                            |  |

| 0100        | 4:1           | 500                   | 125                            |  |

| 0101        | 5:1           | 600                   | 120                            |  |

| 0110        | 6:1           | 600                   | 100                            |  |

| N=7-15      | N:1           | 600                   | 600/N                          |  |

•Upon reset, SSEL[3:0] = 0101

### **PLL Control Register (PLL\_CTL)** Controls operation of the PLL, specifying loop parameters and • global control bits PLL Control Register (PLL\_CTL) 15 14 13 12 11 10 - 9 6 5 з 2 8 7 4 1 0 Reset = 0x14000 0 0 0 0 0 0 0 0 0 0 0 0 0 1 MSEL[5:0] DF (Divide Frequency) (Multiplier Select) 0 - Pass CLKIN to PLL See Table 8-1 on page 8-4 for 1 - Pass CLKIN/2 to PLL CLKIN/VCO multiplication PLL OFF factors 0 - Enable power to PLL BYPASS -1 - Disable power to PLL 0 - Do not bypass the PLL STOPCK (Stop Clock) 1 - Bypass the PLL 0 - CCLK on 1 - CCLK off PDWN (Power Down) 0 - All internal clocks on 1 - All internal clocks off ANALOG DEVICES

- Otherwise, SCLK will be automatically adjusted to fall into compliance, but not necessarily optimized for top allowable speed

- Programmer must ensure SCLK frequency does not exceed 133 MHz

### **Programming PLL Transitions**

- Simply modifying PLL\_CTL bits will not change the PLL operating mode until a specific code sequence executes:

- CLI R0; /\* disable interrupts \*/

- IDLE; /\* drain pipeline and send core into idle state \*/

- STI R0; /\* re-enable interrupts after wakeup \*/

- This sequence is necessary when changes have been made to MSEL, DF, or operating state bits (PDWN, BYPASS, STOPCK)

- However, changes to CSEL or SSEL divide ratios take effect immediately, without needing the above sequence

- If the CLKIN-to-VCO multiplier has been changed, or the PLL has been re-enabled, the PLL will now need to relock

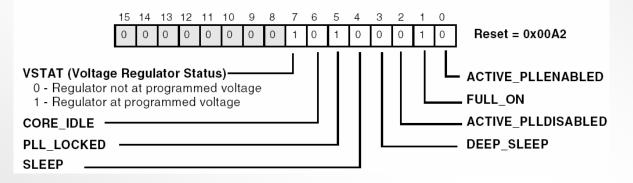

### **PLL Status Register (PLL\_STAT)**

## • PLL\_STAT indicates the operating mode of the PLL and the ADSP-BF533 processor

### PLL Status Register (PLL\_STAT)

Read only. Unless otherwise noted, 1 - Processor operating in this mode. For more information, see "Operating Modes" on page 8-14.

### **Relocking the PLL**

- PLL lock count starts once the IDLE instruction has executed

- PLL lock counter is cleared and then increments each SCLK cycle

- When it reaches the value programmed into the PLL\_LOCKCNT MMR, the PLL\_LOCKED bit is set in PLL\_STATUS

- Then the PLL Wakeup interrupt is asserted, and an interrupt will occur if this interrupt is enabled in SIC\_IMASK

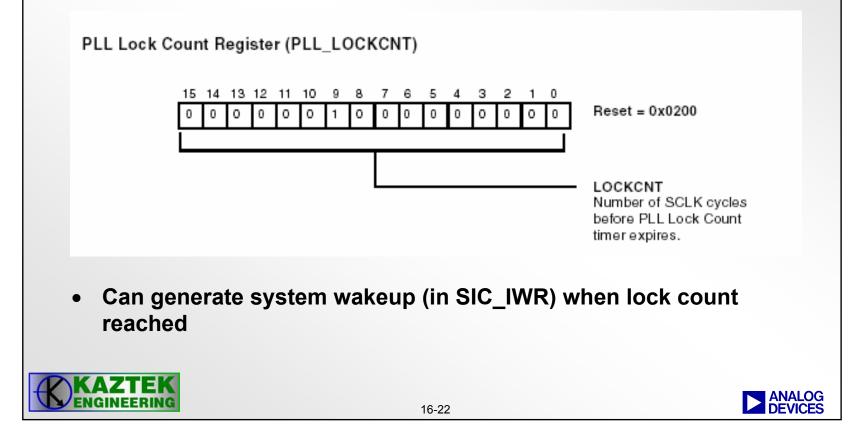

### PLL Lock Count Register (PLL\_LOCKCNT)

• PLL\_LOCKCNT defines the number of SCLK cycles before the PLL\_LOCKED bit (in PLL\_STAT) gets set after a PLL transition

### **IDLE state**

- After executing 'IDLE', an 'SSYNC' instruction automatically occurs.

- The DSP core stops executing instructions, retains the contents of pipeline and waits for an interrupt or wakeup.

- PLL, CCLK and SCLK continue running

- 2 ways to leave an IDLE state

- DSP services an interrupt. DSP will return to the instruction following the IDLE after executing the RTI instruction.

- A peripheral wakes the DSP up (based on SIC\_IWR settings), but no interrupt occurs. DSP returns to instruction that follows IDLE

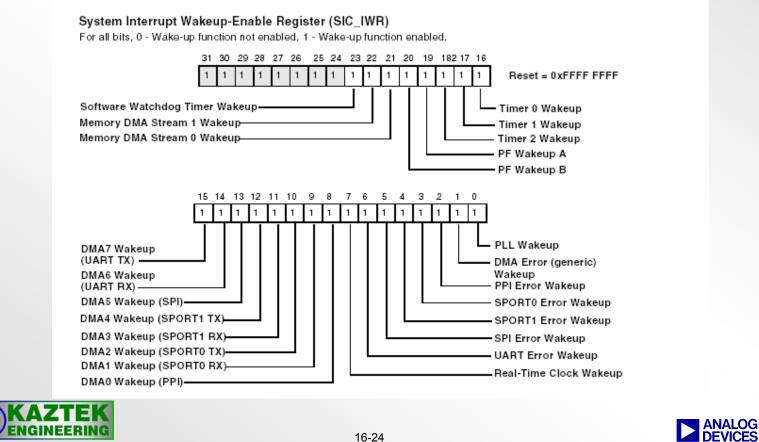

### System Interrupt Wakeup-Enable Register (SIC\_IWR)

• Choose the peripherals that can wake the core from an idle state in SIC\_IWR

### **PLL Control Register (PLL\_CTL)** Controls operation of the PLL, specifying loop parameters and • global control bits PLL Control Register (PLL\_CTL) 15 14 13 12 11 10 - 9 6 5 з 2 8 7 4 1 0 Reset = 0x14000 0 0 0 0 0 0 0 0 0 0 0 0 0 1 MSEL[5:0] DF (Divide Frequency) (Multiplier Select) 0 - Pass CLKIN to PLL See Table 8-1 on page 8-4 for 1 - Pass CLKIN/2 to PLL CLKIN/VCO multiplication PLL OFF factors 0 - Enable power to PLL BYPASS -1 - Disable power to PLL 0 - Do not bypass the PLL STOPCK (Stop Clock) 1 - Bypass the PLL 0 - CCLK on 1 - CCLK off PDWN (Power Down) 0 - All internal clocks on 1 - All internal clocks off ANALOG DEVICES

| A                            | DSP-                                                      | BF533 Voltage Regulator Control Re<br>(VR CTL)                                                                                                                                        | egiste                       | r                                                          |

|------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------------|

| Voltag                       | e Regulator                                               | Control Register (VR_CTL)                                                                                                                                                             |                              |                                                            |

| 0 - RTC<br>1 - RTC<br>VLEV[3 | 0008 0 0<br>Wakeup-enat<br>or Reset wake<br>or Reset wake | Die)       FREQ[1:0] (Voltage Frequency)         eup disabled       Controls the switching oscillator         frequency for the voltage regulator,       see Table 8-10 for encodings | FREQ<br>00<br>01<br>10<br>11 | Value       Powerdown       333KHz       667KHz       1MHz |

| 0000-0101                    | Reserved                                                  |                                                                                                                                                                                       | Gain                         | Value                                                      |

| 0110                         | .85 volts                                                 |                                                                                                                                                                                       | 00                           | 5                                                          |

| 0111                         | .90 volts                                                 |                                                                                                                                                                                       | 01                           | 10                                                         |

| 1000                         | .95 volts                                                 |                                                                                                                                                                                       |                              |                                                            |

| 1001                         | 1.00 volts                                                |                                                                                                                                                                                       | 10                           | 20                                                         |

| 1010                         | 1.05 volts                                                |                                                                                                                                                                                       | 11                           | 50                                                         |

| 1011                         | 1.10 volts                                                |                                                                                                                                                                                       |                              |                                                            |

| 1100                         | 1.15 volts                                                | To bypass the on-chip regulator                                                                                                                                                       |                              |                                                            |

| 1101                         | 1.20 volts                                                |                                                                                                                                                                                       |                              |                                                            |

| 1110                         | 1.25 volts                                                | •Leave the 2 VROUT pins floating                                                                                                                                                      |                              |                                                            |

| 1111                         | 1.30 volts                                                | •Set FREQ[1:0] in VR_CTL to '00'                                                                                                                                                      |                              |                                                            |

| KAZ                          | TEK                                                       | •Connect external 0.8V-1.2V supply to VDDint pi                                                                                                                                       | ns                           |                                                            |

| <b>ENGINE</b>                | ERING                                                     | 16-27                                                                                                                                                                                 |                              | DEVICES                                                    |

### **Resetting the ADSP-BF533**

## **Reset Types**

|                                                                                                                                                                      | Reset                         | Source                                                                                                                                                                                                                                       | Result                                                                                                                                                                                                                                                           |                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

|                                                                                                                                                                      | Hardware reset                | The RESET pin causes a hardware reset.                                                                                                                                                                                                       | Resets both the core and the peripherals,<br>including the Dynamic Power Manage-<br>ment Controller (DPMC).<br>Resets the No Boot on Software Reset bit<br>in SYSCR. For more information, see<br>"System Reset Configuration Register<br>(SYSCR)" on page 3-14. |                                                                                             |

|                                                                                                                                                                      | System Software<br>reset      | Writing b#111 to bits [2:0]<br>in the system MMR SWRST<br>at address 0xFFC0 0100<br>causes a System Software<br>reset.                                                                                                                       | Resets only the peripherals, excluding<br>the RTC (Real-Time Clock) block and<br>most of the DPMC. The DPMC resets<br>only the No Boot on Software Reset bit<br>in SYSCR. Does not reset the core.                                                               | System transitions into<br>boot mode sequence<br>upon completion of                         |

| Both of these SW resets are used rimarily for debugging purposes.                                                                                                    | Watchdog<br>Timer reset       | Programming the watchdog<br>timer appropriately causes a<br>Watchdog Timer reset.                                                                                                                                                            | Resets both the core and the peripherals,<br>excluding the RTC block and most of<br>the DPMC.<br>The Software Reset register (SWRST) can<br>be read to determine whether the reset<br>source was the watchdog timer.                                             | internal reset                                                                              |

| •The system may be in an unreliable<br>state after a SW reset period ends.<br>Therefore, execution must be from<br>L1 memory after a Core or<br>Peripheral SW Reset. | Core Double-<br>Fault reset   | If the core enters a dou-<br>ble-fault state, a reset can be<br>caused by unmasking the<br>Core Double-Fault Reset<br>Mask bit in the System<br>Interrupt Controller (SIC)<br>Interrupt Mask register<br>(SIC_IMASK).                        | Resets both the core and the peripherals,<br>excluding the RTC block and most of<br>the DPMC.<br>SWRST can be read to determine whether<br>the reset source was Core Double-Fault.                                                                               | Coccurs when an<br>exception is<br>generated while<br>another exception<br>is being handled |

|                                                                                                                                                                      | Core-Only Soft-<br>ware reset | Executing a RAISE1 instruc-<br>tion or by setting the Soft-<br>ware Reset (SYSRST) bit in<br>the core Debug Control reg-<br>ister (DBGCTL) via emula-<br>tion software through the<br>JTAG port. DBGCTL is not<br>visible to the memory map. | Resets only the core.<br>The peripherals do not recognize this<br>reset.                                                                                                                                                                                         |                                                                                             |

### **Hardware Reset**

- Asynchronous

- /RESET pin asserted low until after supplies have stabilized

- After pin deasserted, reset timer allows all peripherals to complete a reset

- Interrupt request generated

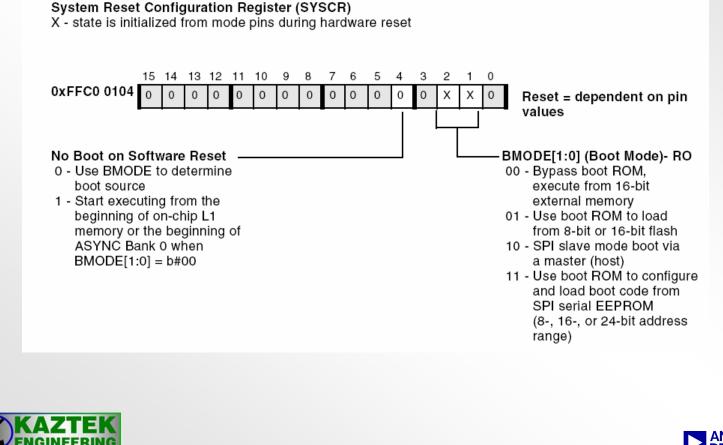

- System then moves into boot mode (based on BMODE pins)

### **Staying in Supervisor Mode after Reset**

- If executing from external memory after hardware reset, the ADSP-BF533 will be in the Reset ISR

- This implies the part is in Supervisor mode, but...

- Lower priority events can not be serviced until you return from Reset ISR

- Customer can force the lowest priority interrupt in order to remain in Supervisor mode

- If booting after hardware reset, the above process is automatically performed by the Boot ROM

### **Supervisor Mode Reset Example**

| /*****Code to                          | Stay in Supervisor Mode************************************                    |                  |

|----------------------------------------|--------------------------------------------------------------------------------|------------------|

| SP.H = 0xF003;                         | //Set up supervisor stack                                                      |                  |

| SP.L = 0xFFDC;                         |                                                                                |                  |

| P0.L =LO(EVT15);                       | //Point to EVT15 in Event Vector Table                                         |                  |

| P0.H = HI(EVT15);                      |                                                                                |                  |

| P1.L = START;                          | //Point to start of Boot Rom code (or any other code)                          |                  |

| P1.H = START;                          |                                                                                |                  |

| [P0] = P1;                             | //Place the address of start code in EVT15 of Event Vector Table               |                  |

| P0.L = LO(IMASK);                      |                                                                                | Used to re-enter |

| R0 = W[P0];                            |                                                                                | Supervisor mode  |

| R1.L = LO(EVT15);                      |                                                                                |                  |

| R0 = R0   R1;                          |                                                                                |                  |

| W[P0] = R0;                            | //Set(enable) EVT15 bit in IMASK Register                                      |                  |

| RAISE 15;                              | //Invoke ET15 interrupt (still in higher-priority ISR, so nothing happens yet) |                  |

| P0.L = WAIT_HERE;                      |                                                                                |                  |

| P0.H = WAIT_HERE;                      |                                                                                |                  |

| RETI = P0;                             |                                                                                |                  |

| RTI;                                   | //Return from Reset Interrupt to allow processing of lower priority interrupts |                  |

| WAIT_HERE:                             | //Wait here till EVT15 interrupt is processed                                  |                  |

| JUMP WAIT_HERE;                        |                                                                                |                  |

| /************************************* | ***************************************                                        |                  |

| START:                                 |                                                                                |                  |

| [SP] = RETI;                           | // Re-enable interrupts                                                        |                  |

| KAZTEK                                 |                                                                                |                  |

| ENGINEERING                            | 16-32                                                                          | DEVICES          |

### **Default Settings after Reset**

| Item                       | Description of Reset State                                  | _                                                      |

|----------------------------|-------------------------------------------------------------|--------------------------------------------------------|

| Core                       |                                                             |                                                        |

| Operating mode             | Supervisor mode in reset event, clocks stopped              |                                                        |

| Rounding mode              | Unbiased rounding                                           |                                                        |

| Cycle counters             | Disabled, zero                                              |                                                        |

| DAG registers (I,L,B,M)    | Random values (must be cleared at initialization)           | - DLL Softings offer Deast (Evenue)                    |

| Data and Address registers | Random values (must be cleared at initialization)           | <ul> <li>PLL Settings after Reset (Example)</li> </ul> |

| IPEND, IMASK, ILAT         | Cleared, interrupts globally disabled with IPEND bit 4      | Assume CLKIN = 25MHz Oscillator                        |

| CPLBs                      | Disabled                                                    |                                                        |

| L1 Instruction Memory      | SRAM (cache disabled)                                       | - MSEL[5:0] = 0x0A, DF = 0                             |

| L1 Data Memory             | SRAM (cache disabled)                                       | VCO = 25MHz x 10 = 250MHz                              |

| Cache validity bits        | Random (must be set to invalid before cache initialization) | CCLK = VCO/1 = 250 MHz                                 |

| System                     |                                                             |                                                        |

| Booting methods            | Determined by the values of BMODE pins at reset             | SCLK = VCO/5 = 50 MHz                                  |

| MSEL clock frequency       | Reset value = 10                                            |                                                        |

| PLL Bypass mode            | Disabled                                                    |                                                        |

| VCO/Core Clock Ratio       | Reset value = 1                                             |                                                        |

| VCO/System Clock Ratio     | Reset value = 5                                             |                                                        |

| Peripheral clocks          | Disabled                                                    |                                                        |

### BF533 System Configuration Reset Register (SYSCR)

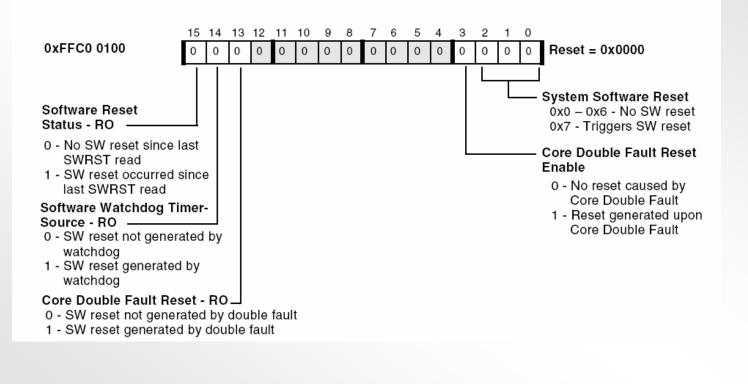

### **Software Reset Register (SWRST)**

Software Reset Register (SWRST)

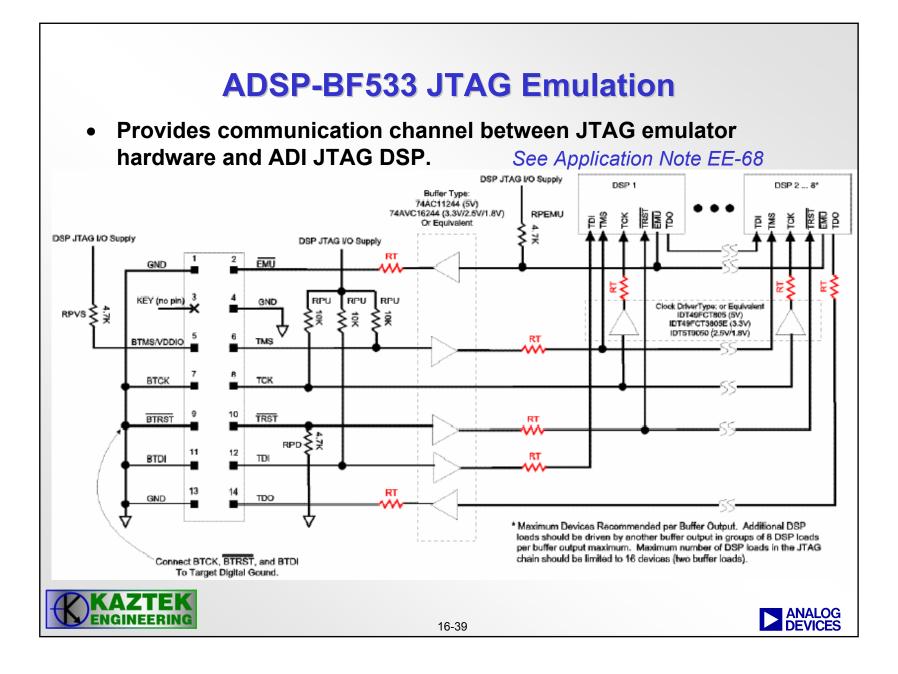

### **JTAG Port**

# **In-Circuit Emulator Support**

- 5-pin JTAG TAP (Test Access Port) allows access to JTAG features

- TAP Controller handles test register event sequencing

- Boundary scan facilitates board-level connectivity testing

- Up to 32 boundary-scan instructions accommodated

# ADSP-BF533 JTAG

- IEEE standard 1149.1-1990

- Boundary Scan (bsdl files available)

- Read Part Identification Code

- Analog Devices JEDEC ID is 0x0E5

- Instruction Register is 5 bits wide

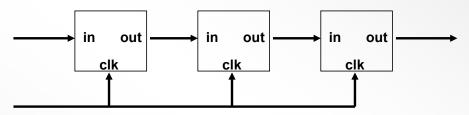

- In Bypass mode behaves like a 1-bit shift register

- Emulation (ADI enhancement)

# **Board Design and Layout**

# What do you need for ADSP-BF533/BF561 Hardware Design?

- ADSP-BF533 DSP Hardware Reference

- Includes Hardware Examples

- The Datasheet ( check the web for latest revision! )

- Insure that all timing requirements are met!!!!

- The Anomaly Sheet ( check the web for latest revision! )

- Use EZ-Kits as Design Example

- Look for Application Notes

- Recommended Reading

High Speed Digital Design - A Handbook of Black Magic Johnson & Graham Prentice Hall,Inc. ISBN 0-13-395724-1

# **Navigating the Datasheet**

- Power Supply and Input Voltage and Temperature Ranges

- ABSOLUTE MAXIMUM RATINGS (When violated, device might be damaged)

- RECOMMENDED OPERATING CONDITIONS (When violated, device might not work properly)

- ELECTRICAL CHARACTERISTICS

- Tested or guaranteed DC characteristics

- TIMING PARAMETERS

- How do Interface Output Pins behave

- What do Interface Input Pins require

- ADDITIONAL DIAGRAMS

- Typical behavior of power consumption and I/O stages

- No guaranteed limits !

# **Powering Up the DSP**

- The ADSP-BF533 has multiple power domains.

- Apply the core supply (VDDINT) first and limit supply current as well as the duration of unpowered I/O to prevent latch-up effects and damage of isolating diodes.

- Never apply external clock to CLKIN pin while DSP is not powered.

| Power Domain       | V <sub>DD</sub> Range |

|--------------------|-----------------------|

| All internal logic | 0.8V(min) -1.2V ± 5%  |

| All I/O            | 2.5-3.3V ± 10%        |

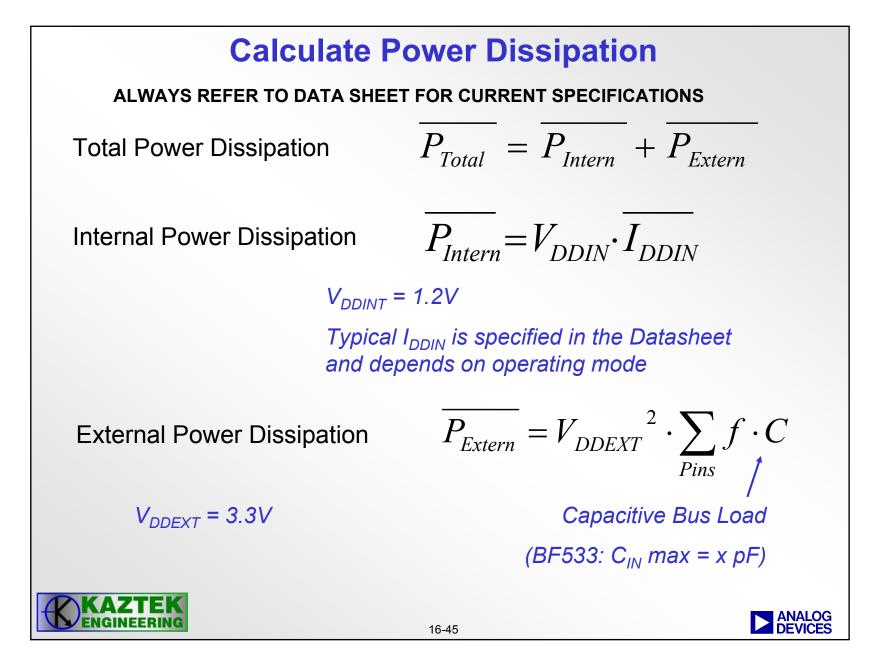

#### **ADSP-BF533 Internal Current Consumption**

- Core Supply IDDINT

- Peak

- Executing from internal memory

- TBD

- Typical

- Executing from internal memory

- 50% are MAC instruction

- Power-down All

- Peripheral Supply IDDINT

- Typical

- Power-down

#### **ALWAYS CHECK DATA SHEET FOR LATEST INFO.**

# **High-Speed Design Issues**

- Awareness of High Speed Digital Design

- Signal Integrity on Wires and Connectors

- Noise generated by Crosstalk

- EMI / EMC Compliance

- Bypassing Capacitors (Ceramic)

- 100nF decoupling capacitors between VddInt and Gnd

- 100nF decoupling capacitors between VddExt and Gnd

- One 100nF capacitor at the power supply connector of the board

- Grounding and Shielding

- Dedicated VDD and GND supply plane recommended

- No Ground Loops

- Signal Return Path as short as possible

- No Signal Routing over Split Planes

### **Advanced Support for Embedded Debug**

- Hardware Breakpoints

- 6 Instruction and 2 Data Watchpoints

- Performance Monitor Unit

- Counters for cycles and occurrences of specific activities

- Execution Trace Buffer

- Stores last 16 non-incremental PC values

# **Reference Material**

System Design

### **Hardware Breakpoints**

- 8 Watchpoints for Instruction/Data Address Comparison

- 6 Instruction Watchpoints, 2 Data Watchpoints

- Can be used as 4 Watchpoint ranges instead (3 instruction address ranges + 1 data address range)

- Allow conditional program halting, based on user-specified conditions

- Memory accesses within a specified range

- Data loaded into register

- Stack activity

- Counter allows tracking of watchpoint events

- Ability to combine events

- Break ONLY when ALL or when ANY enabled events occur

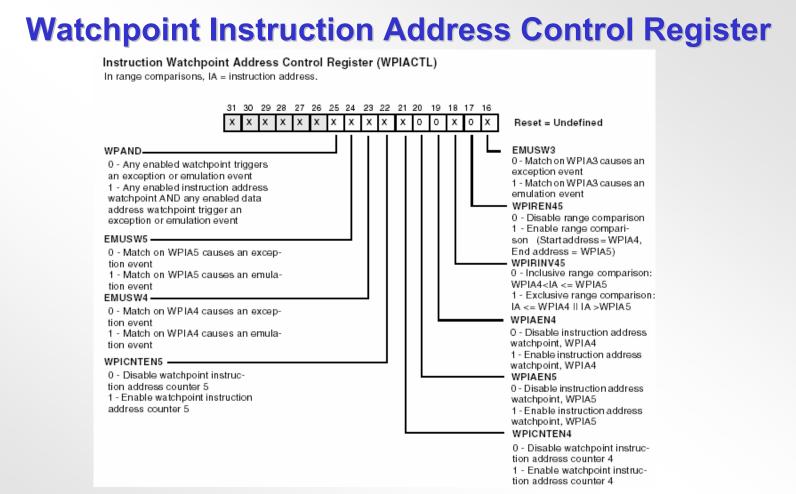

# Watchpoint Control Registers

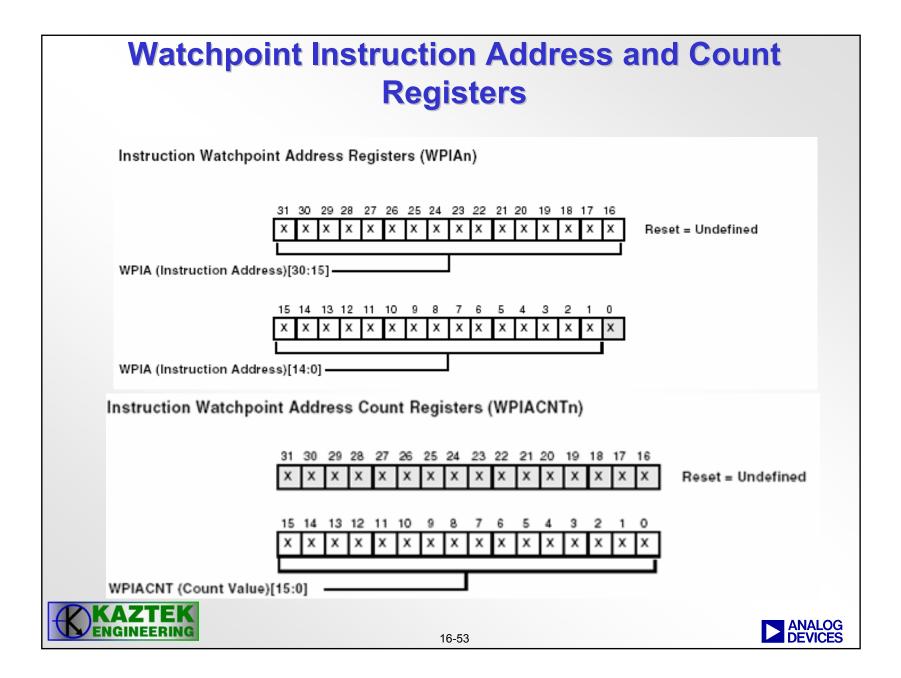

The Watchpoint Unit contains these MMRs, which are accessible in Supervisor and Emulator modes:

- The Watchpoint Status register (MPSIAI)

- Six Watchpoint Instruction Address registers (WPIA[5:0])

- Six Watchpoint Instruction Address Count registers (WPIACNT[5:0])

- The Watchpoint Instruction Address Control register (WPIACTL)

- Two Watchpoint Data Address registers (WPDA[1:0])

- Two Watchpoint Data Address Count registers (NPDACNT[1:0])

- The Watchpoint Data Address Control register (WPDACTL)

Bits 0-15 of WPIACTL (not shown) control remaining instruction

#### watchpoints

## Watchpoint Data Registers

Analogous set of registers exist for two Data Watchpoints

Each data watchpoint is controlled by four bits in the WPDACTL register:

| Bit Names | Description                                                                                                                  |

|-----------|------------------------------------------------------------------------------------------------------------------------------|

| WPDACCx   | Determines whether the match should be on a tead or write access.                                                            |

| WPD8RCx   | Determines which DAG the unit should monitor.                                                                                |

| WPDCNTENs | Enables the counter that counts the number of address matches. If the counter is disabled, then every match causes an event. |

| WPDAENx   | Enables the data watchpoint activity.                                                                                        |

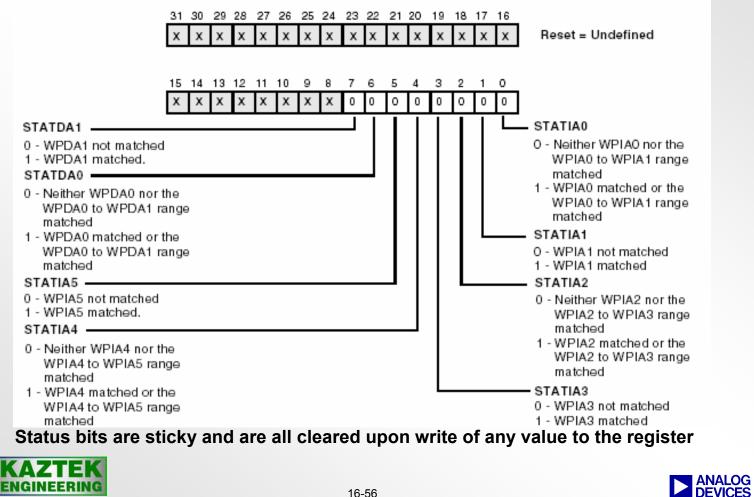

# Watchpoint Status Register

Watchpoint Status Register (WPSTAT)

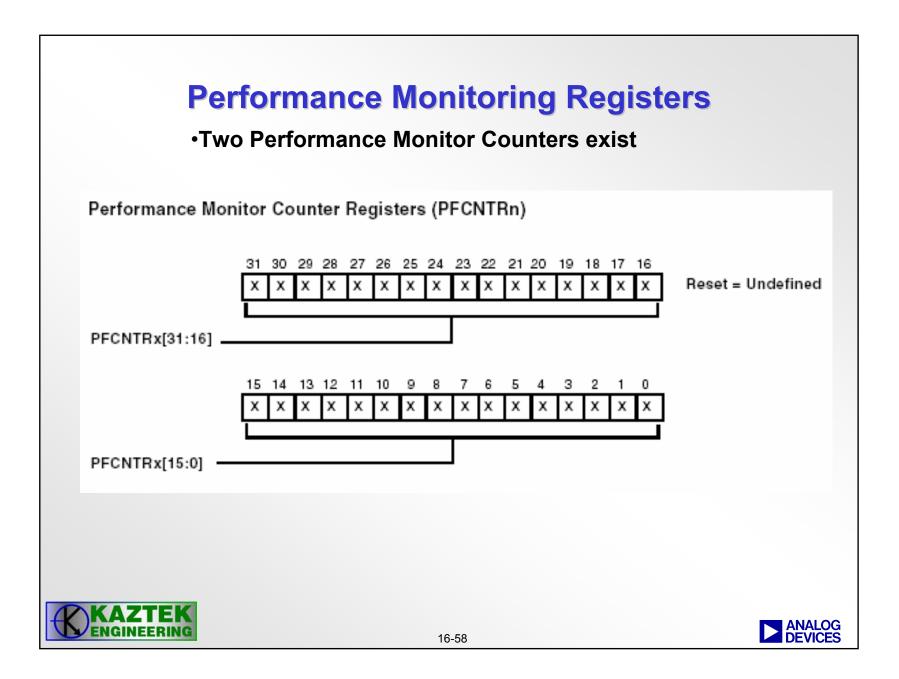

### **Performance Monitoring**

- Dedicated registers available for system tuning and load balancing

- Includes two 32-bit counters, and registers to count number of cycles or occurrences of an event

- Unit accesses (MAC0, MAC1, DAG0, DAG1)

- Branches and exceptions

- Memory conflicts

- Loads/stores (8/16/32-bit)

- Cache hits and misses

- Interrupt latencies

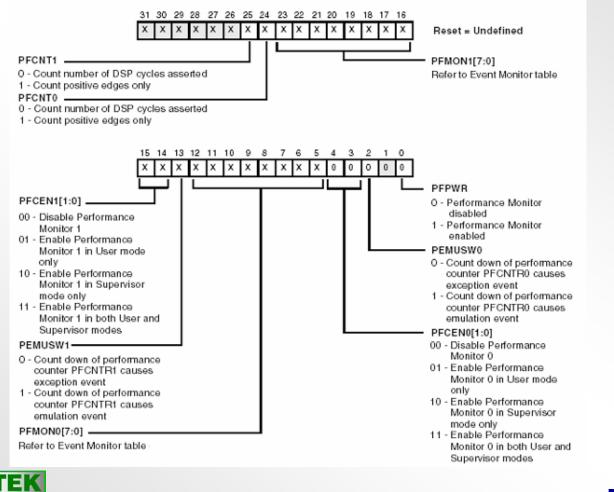

#### **Performance Monitor Control**

Performance Monitor Control Register (PFCTL)

#### What can be counted?

| PFMONx Fields | Events That Cause the Count Value to Increment                     | PFMONx Fields | Events That Cause the Count Value to Increment                                                                                                                                                   |

|---------------|--------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00          | Loop 0 iterations                                                  | 0x83          | Data memory write buffer full stalls due to high to low priority code transition                                                                                                                 |

| 0x01          | Loop 1 iterations                                                  | 0x84          | Data memory store buffer forward stalls due to lack of                                                                                                                                           |

| 0x02          | Loop buffer 0 not optimized                                        | UXU1          | committed data from processor                                                                                                                                                                    |

| 0x03          | Loop buffer 1 not optimized                                        | 0x85          | Data memory fill buffer stalls                                                                                                                                                                   |

| 0x04          | PC invariant branches                                              | 0x86          | Data memory array or TAG collision stalls (DAG to DAG, or DMA to DAG)                                                                                                                            |

| 0x06          | Conditional branches                                               | 0x87          | Data memory array collision stalls (DAG to DAG or DMA to DAG)                                                                                                                                    |

| 0x09          | Total branches (calls, returns, branches, but not inter-<br>rupts) |               |                                                                                                                                                                                                  |

|               |                                                                    | 0x88          | Data memory stalls                                                                                                                                                                               |

| 0x0A          | Stalls due to CSYNC, SSYNC                                         | 0x89          | Data memory stalls sent to processor                                                                                                                                                             |

| 0x0B          | EXCPT instructions                                                 | 0x8A          | Data memory cache fills completed to Bank A                                                                                                                                                      |

| 0x0C          | CSYNC, SSYNC instructions                                          | 0x8B          | Data memory cache fills completed to Bank B                                                                                                                                                      |

| 0x0D          | Committed instructions                                             | 0x8C          | Data memory cache victims delivered from Bank A                                                                                                                                                  |

| 0x0E          | Interrupts taken                                                   | 0x8D          | Data memory cache victims delivered from Bank B                                                                                                                                                  |

|               |                                                                    | 0x8E          | Data memory cache high priority fills requested                                                                                                                                                  |

| 0x0F          | Misaligned address violation exceptions                            | 0x8F          | Data memory cache low priority fills requested                                                                                                                                                   |

| 0x10          | Stall cycles due to read after write hazards on DAG registers      | 0x90          | Code memory fetches postponed due to DMA colli-<br>sions (minimum count of two per event)                                                                                                        |

| 0x13          | Stall cycles due to RAW data hazards in computes                   | 0x91          | Code memory TAG stalls (cache misses, or FlushI<br>operations, count of 3 per FlushI). Note code memory<br>stall results in a processor stall only if instruction<br>assembly unit FIFO empties. |

| 0x80          | Processor stalls to memory                                         |               |                                                                                                                                                                                                  |

| 0x81          | Data memory stalls to processor hidden by processor                | -             |                                                                                                                                                                                                  |

|               | stall                                                              | 0x92          | Code memory fill stalls (cacheable or non-cacheable).<br>Note code memory stall results in a processor stall only<br>if instruction assembly unit FIFO empties.                                  |

| 0x82          | Data memory store buffer full stalls                               |               |                                                                                                                                                                                                  |

|               |                                                                    | 0x93          | Code memory 64 bit words delivered to processor instruction assembly unit                                                                                                                        |

### **Performance Monitoring: Cycle Counters**

- All cycles are counted

- Counters stop during Emulation

- Can be read in all operating modes

- Can only be written in the Emulator or Supervisor modes

- Must be enabled to use

```

Example Code for Turning on Cycle Counters

R2 = 0;

CYCLES = R2;

CYCLES2 = R2;

R2 = SYSCFG;

BITSET(R2,1);

SYSCFG = R2;

/* Insert code to be benchmarked here. */

```

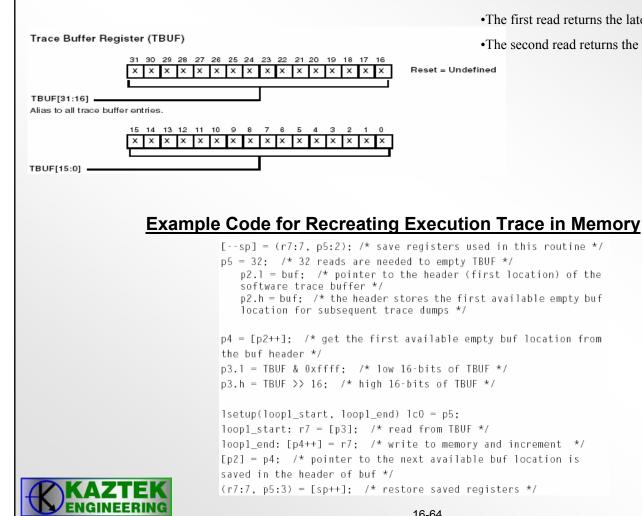

### **Execution Trace**

- 16-entry trace buffer stores changes in program flow (noncontiguous addresses)

- Jumps

- Calls

- Interrupts

- Used for recent-history examination

- Zero-overhead hardware loops register only once in the trace buffer

#### **Trace Buffer Registers** Trace Buffer Control Register (TBUFCTL) 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 х х х х х х х х х х Reset = Undefined х х х х 15 14 13 12 11 10 9 8 7 6 5 2 4 з 1 0 х 0 0 0 0 0 х х х х х х х х TBUFPWR 0 - Trace buffer is active CMPLP[1:0] -1 - Trace buffer is off 00 - Compression disabled Record all discontinuities TBUFEN 01 - Compress single-level 0 - Trace buffer disabled loops 1 - Trace buffer enabled 10 - Compress two-level loops TBUFOVF 0 - Overflows are ignored 1 - Trace buffer overflow causes an exception event Trace Buffer Status Register (TBUFSTAT) 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 Reset = Undefined х х х х х x х х х х х х х х х х 15 14 13 12 11 10 9 8 76 - 5 4 з 2 1 0 х х х х х х х 0 0 0 0 0 TBUFCNT[4:0] -Number of valid discontinuities stored in the trace buffer ANALOG DEVICE

#### **Accessing the Trace Buffer**

•The first read returns the latest branch target address.

•The second read returns the latest branch source address